UART通用异步串口设计开题报告

2020-02-18 19:23:37

1. 研究目的与意义(文献综述)

通用异步收发传输器uart,是设备间进行异步通信的关键模块。uart负责处理数据总线和串行口之间的串/并、并/串转换,并规定了帧格式;通信双方只要采用相同的帧格式和波特率,就能在未共享时钟信号的情况下,仅用两根信号线(rx 和tx)就可以完成通信过程,因此也称为异步串行通信。

uart提供了rs-232c数据终端设备接口,这样计算机就可以和调制解调器或其它使用rs-232c接口的串行设备通信了。作为接口的一部分,uart还提供以下功能: 将由计算机内部传送过来的并行数据转换为输出的串行数据流。将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。在输出数据流中加入启停标记,并从接收数据流中删除启停标记。可以处理计算机与外部串行设备的同步管理问题。uart协议是数据通信及控制系统中广泛使用的一种全双工串行数据传输协议,在实际工业生产中有时并不使用其全部功能,只需将其核心功能合成即可。波特率发生器、接收器和发送器是三个核心功能模块,利用verilog语言对这三个功能模块进行描述并加以整合,从而使整个设计更加紧凑稳定。

如今经济社会高速发展,uart接口也有了新的应用。文献[1]中基于fpga设计平台,为使用freescale公司mcf52259处理器的通用工业控制板配置一个扩展版,以实现主控板对pc/104总线的兼容和多路uart的扩展。利用高速率的多uart可以方便高效的进行多cpu通信,同时还能降低系统成本。文献[2]设计了一款高速和安全的外接接口来对信息进行安全存储。该接口通信时钟与系统时钟来自不同时钟域,实现了跨时钟域设计。该接口是基于总线接口的设计,可以支持字节(8位)、半字(16位)、字(32位)的访问,提高了模块的可移植性,方便对不同功能的寄存器的访问。同时支持低功耗模式,提高了产品优势。文献[3]中采用smic 0.13μm cmos工艺,在3.3v pad供电电压和1.2v core供电电压下,基于低分辨率时钟预比例器结构,设计了一款波特率可达5 mbps的双通道uart。采用低分辨率时钟预比例器结构,利用有理数分频来取代整数分频,可以很大程度上扩宽波特率的范围,提高uart性能和传输精度。同时,多通道设计可使多个通道同时收发数据,大大提高了数据传输速度。为了降低cpu的开销,为发送模块和接收模块各自设计了一个64字节大小的fifo,在dma操作的配合下可实现字符块传输。

2. 研究的基本内容与方案

(1)设计目标

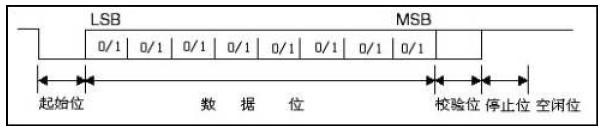

为了方便fpga 和cpu 或者其他设备之间的数据传输,实现一个可编程的通用异步收发器( uart) 模块。支持数据格式:起始位(1bit) 数据(8bit) 奇偶校验位(1bit) 终止位(1bit);奇偶校验可配置;可配置支持115200以下的常见波特率;支持115200以下的波特率自适应;自动计算校验位用于发送数据;对接收不正常的数据应能自动识别并设置错误标志、丢弃。如图1所示:

3. 研究计划与安排

第1-3周 搜集资料,撰写开题报告;

第4-6周 学习使用设计及综合仿真软件;学习verilog语言;熟悉fpga开发板;

第7-11周 设计分频器、数据发送、数据接收模块;集成三大模块并仿真综合;并测试uart与pc通信的正确性;

4. 参考文献(12篇以上)

[1]吴小虎.基于fpga的pc/104和多路uart扩展系统的研究与开发[d]。安徽:安徽大学,2011 .

[2]高宇.安全soc芯片uart接口的设计与实现[d]. 辽宁:辽宁大学,2016 .

[3]魏代德.基于0.13μm cmos工艺的双通道uart芯片设计[d]. 四川: 电子科技大学,2015 .