基于FPGA的高速实时数据采集系统的设计和实现外文翻译资料

2022-08-10 19:33:42

英语原文共 6 页,剩余内容已隐藏,支付完成后下载完整资料

基于FPGA的高速实时数据采集系统的设计和实现

中图分类号 TP335 文档类型 A 文章ID 1005-8885 (2006) 04-0061-06

摘要 在电脑工作时产生的电磁辐射被恢复后会导致信息泄露。本文提出了一种基于外围组件互连(PCI)总线和现场可编程门阵列(FPGA)抽样电磁辐射引起的视频信号的高速实时数据采集系统。对每个模块的硬件设计和控制流程作了详细介绍。采样率可以达到64Msps,通过使用时间交错,系统传输速度可达到128 Mb/s,通过并行操作两个数据转换器从而增加整个系统的采样速度。

关键词 高速数据采集,FPGA,PCI总线,超高速集成电路硬件描述语言(VHDL),模拟-数字转换器(ADC)

1绪论

电气设备会产生电磁辐射,尤其是视频显示单元、工程和可以产生电磁泄漏的设备。当电磁泄漏被发现之后,可用的信息可以被恢复。这将会导致信息泄漏。首先,通过宽带天线接收到电磁辐射。然后,通过同步低通滤波ADC转换为数字形式。最后,从电磁泄漏恢复的数字信息可经过软件方法、相位锁定、相关过滤识别和重建处理后被获取。在本文中,数据采集系统必须接收视频信号的电磁辐射并转换成数字形式。

根据奈奎斯特定理,数字化采样一个正弦波信号至少需要两个数据周期。在本文中,视频格式为640times;480 @75 Hz,像素时钟频率是

因此,采样率必须是64 MHz。一般来说,高速数据采集系统的作用是接受数据和使用直接存储器存取(DMA)机制传输输入字节流到主机内存。近几年来,随着FPGA和PCI的快速发展,通过提供一个公共硬件和主机接口,可以消除对专用硬件的需求。通过对FPGA上数据采集卡[5-8]进行简单的编程,就可以实现应用程序特性的多样性。本文介绍了一种基于Altera Cyclone和Plx PCI9052的数据采集系统。

本文的其余部分组织如下:第二章简要描述系统的设计。第三章介绍了电磁兼容性(EMC)技术被用于印刷电路板的设计。最后,得出结论。

2数据采集系统的简要设计

2.1系统框图

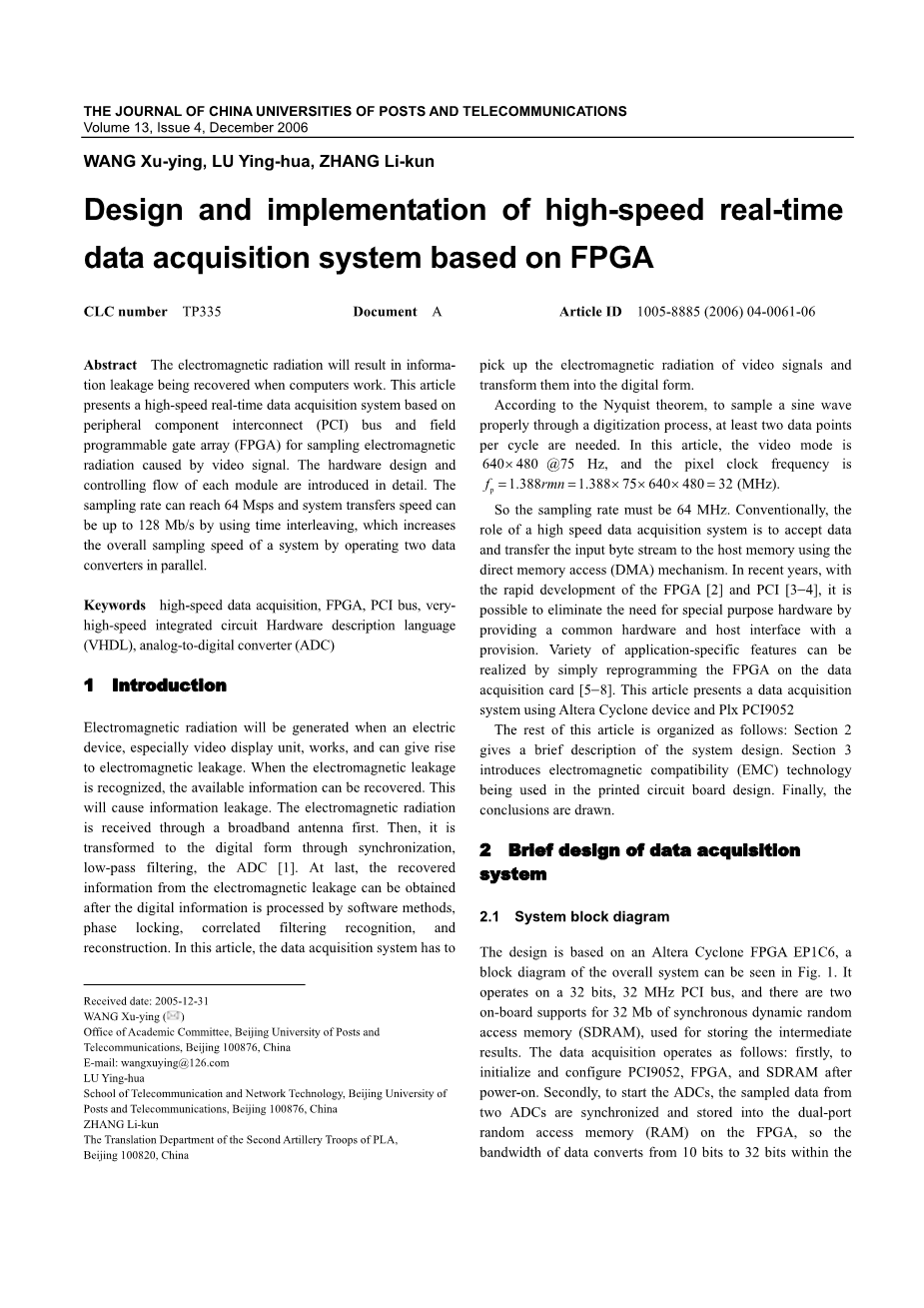

本设计基于Altera Cyclone FPGA EP1C6,整个系统的结构图如图1所示。它运行于一个32位、32MHz的PCI总线上,并且片上有两个32Mb的同步动态随机访问内存(SDRAM)的支持,用以存储中间结果。数据采集操作如下:首先,接通电源后初始化和配置PCI9052、FPGA和SDRAM。其次,启动两个ADC,两个ADC的采样数据被同步和储存进FPGA的双端口随机存取存储器(RAM)上,所以数据的带宽在FPGA内从10位转换为32位。然后,采样信号被存储到SDRAM中。接下来,从SDRAM中读取32位的数据在FPGA中写入,并通过PCI局部总线传输到主机上。下一节将详细描述系统的逻辑设计。

图1 数据采集系统的结构图

2.2 A /D转换

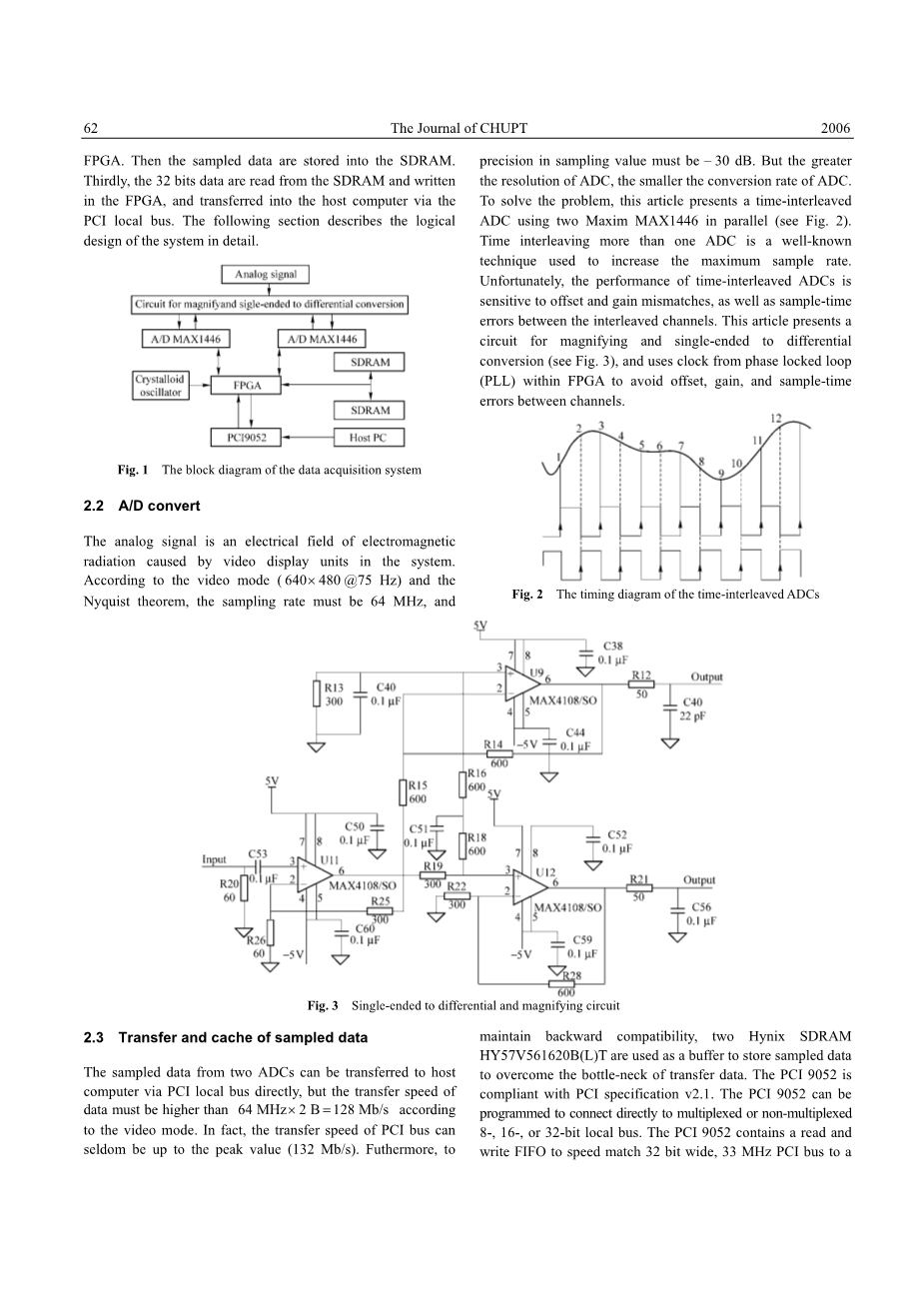

模拟信号是一个系统中由视频显示单元引起的电磁辐射电场。根据视频格式(640times;480 @75Hz)和奈奎斯特定理,采样率必须是64MHz,采样精度必须是-30dB。但是ADC的分辨率越高,转化率就越低。为了解决这个问题,本文提出了一种使用两个MAX1446并行的分时ADC(见图2)。使用时间交错多个ADC是一个众所周知的技术,用于提高最大采样率。不幸的是,分时ADC的性能对交错通道间的偏移和增益不匹配非常敏感。本文提出了一种单端差分放大电路(见图3),使用FPGA内锁相环(PLL)的时钟来避免偏移、增益和不同通道间采样时间的偏差。

图2 分时ADC的时序图

图3 单端差分放大电路

2.3采样信号的转换与缓存

两个ADC的采样信号可以通过PCI局部总线直接传输到主机中,但是根据视频格式,传输速率必须高于64MHztimes;2B=128Mb/s。实际上,PCI总线的传输速率很少能够达到峰值(132Mb/s)。此外,为了保持反向兼容性,使用两个Hynix SDRAM HY57V561620B(L)T作为缓冲存储采样数据,克服传输数据的瓶颈。PCI 9052兼容PCI规范v2.1。PCI 9052可以通过编程直接连接到多路复用或非多路复用的8、16或32位局部总线。PCI 9052包含一个读写FIFO来匹配32位宽、33MHz的PCI总线到局部总线,局部总线可能更窄或更慢。最多可以支持五个局部地址空间和四个片选。本设计中局部总线的脉冲长度为8。局部总线运行于32位、32MHz、三个局部地址空间和两个片选。

2.4 FPGA的逻辑设计

在本文中,与应用程序有关的控制功能以及SDRAM、ADC,、PCI接口都是由FPGA逻辑处理。FPGA的逻辑整体设计图4所示。整个逻辑设计包括时钟模块、SDRAM读写模块和SDRAM控制器模块。

图4 FPGA的逻辑设计

2.4.1时钟模块

Cyclone FPGA EP1C6提供了一个全局时钟网络和两个锁相环作为一个完整的时钟管理解决方案。Cyclone锁相环提供一般时钟和时钟乘法和除法、可编程相移、可编程占空比和输出差动I/O支持。设计者可以使用Quartus II软件自动设置相移、占空比以及最小化外部时钟输出的抖动。由于分时ADC的性能对交错通道间的偏移和增益不匹配非常敏感,因此作为系统时钟的信号应该具有最低的相位抖动和噪声。在本文中,时钟模块利用锁相环和驱动全局时钟网络来改善系统的性能。图5显示了使用VHDL编程的Quartus II软件的时钟模块的框图。

图5 时钟模块的框图

是32 MHz频率的时钟,作为ADC驱动时钟。和单倍频,它们的相位相反。是三倍频,96MHz作为SDRAM的驱动时钟。

2.4.2 SDRAM读写模块

SDRAM读写模块包含三个主要模块,SDRAM写模块、SDRAM读模块和SDRAM设备初始化和SDRAM读写指令模块。SDRAM读写模块是顶层模块,使整个设计连接在一起。SDRAM写模块从两个ADC获取采样信号,然后将它们转换为32位,等待SDRAM设备初始化和SDRAM读写指令模块的写SDRAM指令,将其接入SDRAM。SDRAM读模块等待SDRAM设备初始化和SDRAM读写指令模块的读SDRAM指令去读取SDRAM,然后将采样数据输出到PCI局部总线。SDRAM设备初始化和SDRAM读写指令模块向SDRAM控制器生成初始化指令和配置寄存器指令,允许两个ADC采样数据,向SDRAM读模块生成读SDRAM命令,向SDRAM写模块生成写SDRAM命令,并提供SDRAM地址总线。在FPGA实现中,整体设计中,逻辑元素占5%,一个锁相环和嵌入式内存占80%。SDRAM读写模块的顶层系统框图可使用Quartus II软件用VHDL表示,如图6所示。

图6 SDRAM读写模块的框图

SDRAM写模块和SDRAM读模块均由页面地址生成器和双端口RAM组成。Cyclone FPGA EP1C6提供了20块M4K嵌入式RAM。M4K模块支持双端口存储。Quartus II软件可以通过连接多个M4K内存块自动实现更大的内存。页地址生成器可由Quartus II软件使用VHDL实现。使用VHDL实现页地址生成器的代码如下:

process(wclk,wen)—RAM written process

begin

if (wen = 1) then

if wclkevent and wclk = 1 then

if (wtmp = '1111111111') then

wtmp lt;= '0000000000';

else

wtmp lt;=wtmp 1;

--wtpm is value of write address

end if;

else null;

end if;

else null;

end if;

if( ('0000000000' lt;= wtmp and wtmp lt;= '0111111111') or ('0000000000' lt;= rtmp and rtmp lt;= '0111111111') )then pagelt;=0;

else page lt;= 1;

end if;

if(wtmp = '0111111111' or wtmp = '1111111111')then

page_full lt;= 1;

else page_full lt;= 0;

end if;

end process;

process(rclk,en) -- RAM read process

begin

if (en = 1) then

-- if(page = 0)then rtmp lt;= 0;

if ( rclkevent and rclk = 1 )then

if (rtmp = '1111111111') then rtmp lt;='0000000000';

else

rtmp lt;= rtmp 1;

end if;

else null;

end if;

else null;

end if;

if(rtmp = '0111111111' or rtmp = '1111111111')then page_empty lt;= 1;

else page_empty lt;= 0;

end if;

end process;

2.4.3 sdram控制器模块

SDRAM是由高速动态随机存储器(DRAM)与同步接口组成。如果使用效率很高的话,SDRAM的同步接口和完全流水线的内部架构允许非常快的数据速率。SDRAM由使用RASN、CASN和WEN信号组合形成的总线命令控制。必须先打开SDRAM库,然后才能对一系列地址进行读写。用于访问SDRAM的主要命令是读(RD)和写(WR)。当发出WR指令时,将注册初始列地址和数据字。当发出RD指令时,将注册初始地址。经过1-3个时钟周期后,初始数据会传送到数据总线上。自动更新指令会周期性的发出,以确保数据被保留。这些机制都是由SDRAM控制器执行。SDRAM控制器主要由四部分组成,SDRAM控制器、控制接口、指令和数据路径模块。控制接口模块从SDRAM设备初始化和SDRAM读写指令模块获取指令和相关的存储器地址,对指令进行解码,并将请求传递给指令模块。指令模块从控制接口模块获取指令和地址,为SDRAM生成适当的指令。数据路径模块在读和写指令之间处理数据路径操作。SDRAM控制器的框图如图7所示。

图7 SDRAM控制器模块的框图

SDRAM控制器模块设计使用有限状态机(FSM)。SDRAM控制器模块的FSM如图8所示。SDRAM控制器模块可在Quartus II中使用VHDL实现。

图8 SDRAM控制器中的FSM

3 印刷电路板设计中的EMC

高速实时数据采集系统电路由模拟电路和数字电路组成。当高速实时数据采集系统工作时,会产生电磁辐射,引起电磁干扰(EMI),从而对系统性能产生影响。本文中,下面的EMC技术被运用在印刷电路板(PCB)设计中以减少系统的电磁干扰。

1)四层板与分割接地和电源层产生最高水平的信号完整性。信道在顶部和底部的平面上被路由,并且它们是垂直的,以避免相互感应造成的电磁干扰。

2)分割接地和电源层,匹配模拟地和数字地的物理位置以及模拟电源和数字电源。分割数字电源,匹配接地的5V和-5V(PCI电源引脚),3.3V(FPGA,SDRAM和ADC电源引脚)和1.5V(FPGA电源引脚)。这两个电源层单点连接,这样数字地的噪声电流就不能干扰模拟地层面。高速数字信道就被从敏感的模拟信号(比如ADC参考输入、参考间电压输出等)中分离出来。

3)所有的旁路电容,使用表面贴装器件,尽可能得靠近设备,最好与ADC同侧以保证有最小的电感。遵循相同的规则,以绕过数字电源到数字地。

4)所有并行信号都满足3W规则,即两信道之间的间隔是信道宽度的三倍。时钟信道与保护信道被从敏感的模拟信道中分离出来,屏蔽电磁干扰对敏感信道的影响。

4结论

本文提出了一种基于PCI总线和FPGA的高速实时数据采集系统,用于采集视频信号引起的电磁辐射。对于超高速应用,并行操作两个ADC,利用时间交错提高了系统整体的采样速率。在系统中,FPAG起到了至关重要的作用,与应用程序有关的控制功能以及SDRAM、ADC和PCI接口都由FPAG逻辑处理。系统经过测试,采样速率可以达到64Msps,系统的转换速率可以达到128MB/s。该系统可连续工作20分钟。

致谢

该项目获得国家自然科学基金(60331010、6027

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[238002],资料为PDF文档或Word文档,PDF文档可免费转换为Word