用于实时 FPGA 编译的坚固核心虚拟 FPGA外文翻译资料

2023-06-15 17:08:14

英语原文共 16 页,剩余内容已隐藏,支付完成后下载完整资料

用于实时 FPGA 编译的坚固核心虚拟 FPGA

介绍

即时(JIT)编译已在许多应用程序中使用,以使标准软件二进制文件能够在不同的底层处理器架构上执行,从而产生软件可移植性的好处。研究人员之前引入了标准硬件二进制的概念,以实现硬件类似的可移植性好处,使用JIT编译器将硬件二进制编译到FPGA。JIT编译器包括技术映射、放置和路由算法的精益版本,这些算法在一个专门为JIT编译而设计的简单的自定义FPGA结构上实现了标准的硬件二进制文件。虽然开发自定义FPGA对于某些应用程序可能是可行的,但我们建议将简单的FPGA结构实现为虚拟FPGA。在本文中,我们提出了一个虚拟FPGA,使用结构VHDL进行描述,从而表示一个设计师可以合成到现有FPGA上的公司核心FPGA。我们将公司核心的虚拟FPGA合成到Xilinx斯巴达的物理FPGA上,然后将18个基准电路映射到虚拟FPGA上。我们的结果显示,与直接将电路映射到物理FPGA结构相比,虚拟FPGA方法的性能降低了6倍,硬件资源使用量增加了100倍。虽然硬件开销很大,但大型商业FPGA容量可能仍然意味着,如果可移植性比资源利用率更重要,一些应用程序可以利用虚拟FPGA方法。此外,我们的工作为未来的虚拟FPGA方法提供了一个基准,这些方法可能通过各种方法降低性能或区域开销。

现场可编程门阵列(FPGAs)的即时(JIT)编译支持开发一个标准的硬件二进制文件,以及新的技术,如翘曲处理[13]。标准的硬件二进制文件将提供可移植性,允许设计者使用单个硬件网表来配置具有不同底层架构的多个不同的FPGA。支持JIT的FPGA编译将能够透明地将标准硬件二进制文件映射到FPGA的可配置逻辑,同时优化该特定FPGA的硬件设计。

在软件设计中,即时编译提供了强大的好处。即时编译包括将软件二进制格式下载到芯片上,然后动态透明地将二进制重新编译到该芯片上特定处理器的指令集。其主要好处是二进制可移植性——标准工具可以用来创建二进制,并且相同的二进制可以下载到许多不同的平台上。现代的x86处理器,包括英特尔的奔腾和Transmeta的Crusoe和效应处理器,合并了JIT编译,其中x86二进制文件被动态转换到芯片的底层RISC或VLIW指令集并进行优化。

FPGA继续找到进入更多的终端产品,如电视机顶盒、手机、医疗设备等,“二进制”的概念变化从一个微处理器程序,更一般的概念平台二进制芯片提供配置位,可能提供FPGA的配置,软件程序,或两者兼而有之。理想情况下,设计者可以为一个FPGA创建一个标准二进制文件,然后将该标准二进制文件映射到任何多个FPGA体系结构中。不幸的是,目前还不存在针对FPGA的标准硬件二进制文件的概念。网表格式特定于特定的FPGA体系结构,而FPGA体系结构的差异很大。

以一个电视机顶盒为例。有线电视公司可以通过下载新的软件二进制文件来透明地升级这些盒子内的软件。即使新的盒子可能包含更高级版本的微处理器,这也可以工作,因为新的处理器通常支持旧的二进制文件或二进制文件可以被JIT编译到不同的处理器。然而,这样的盒子越来越依赖FPGAs来进行视频处理,因此理想情况下,作为平台二进制文件的一部分,我们也可以为FPGAs下载新的硬件二进制文件,以添加新特性或修复bug。然而,较新的盒子可能包含较新的或不同的FPGA架构,从而使升级复杂化。,通过在中合并一个JIT编译器FPGA,一个标准的硬件二进制文件,可以传输和JIT编译到不同的FPGA。

针对FPGA的JIT编译对于执行动态硬件/软件分区[13]的扭曲处理器实际上也是必不可少的。Warp处理器通过将软件内核移动到芯片上的可配置逻辑来动态优化一个执行中的软件二进制文件,从而获得更好的性能和更低的能耗。在扭曲处理器的核心是,需要一个JIT编译器来将合成的硬件电路实现到芯片上可配置的逻辑结构上。

JITFPGA编译的另一个潜在应用可能是未来的台式机、笔记本电脑和手持电脑,这些电脑允许用户将FPGA添加到他们的计算系统中,以提高性能。与今天的计算机用户通过添加RAM来扩展可用内存类似,用户可以简单地插入额外的FPGA资源,或者插入使用更广泛的硬件资源的速度更快的FPGA设备。假设是一个标准的硬件二进制,操作系统可以重新实现硬件二进制或平台二进制,以利用新添加的FPGA。一个受益于额外FPGA资源的示例应用程序可能是指纹或语音识别,为此,添加FPGA可能会将速度从几分钟提高到几秒。

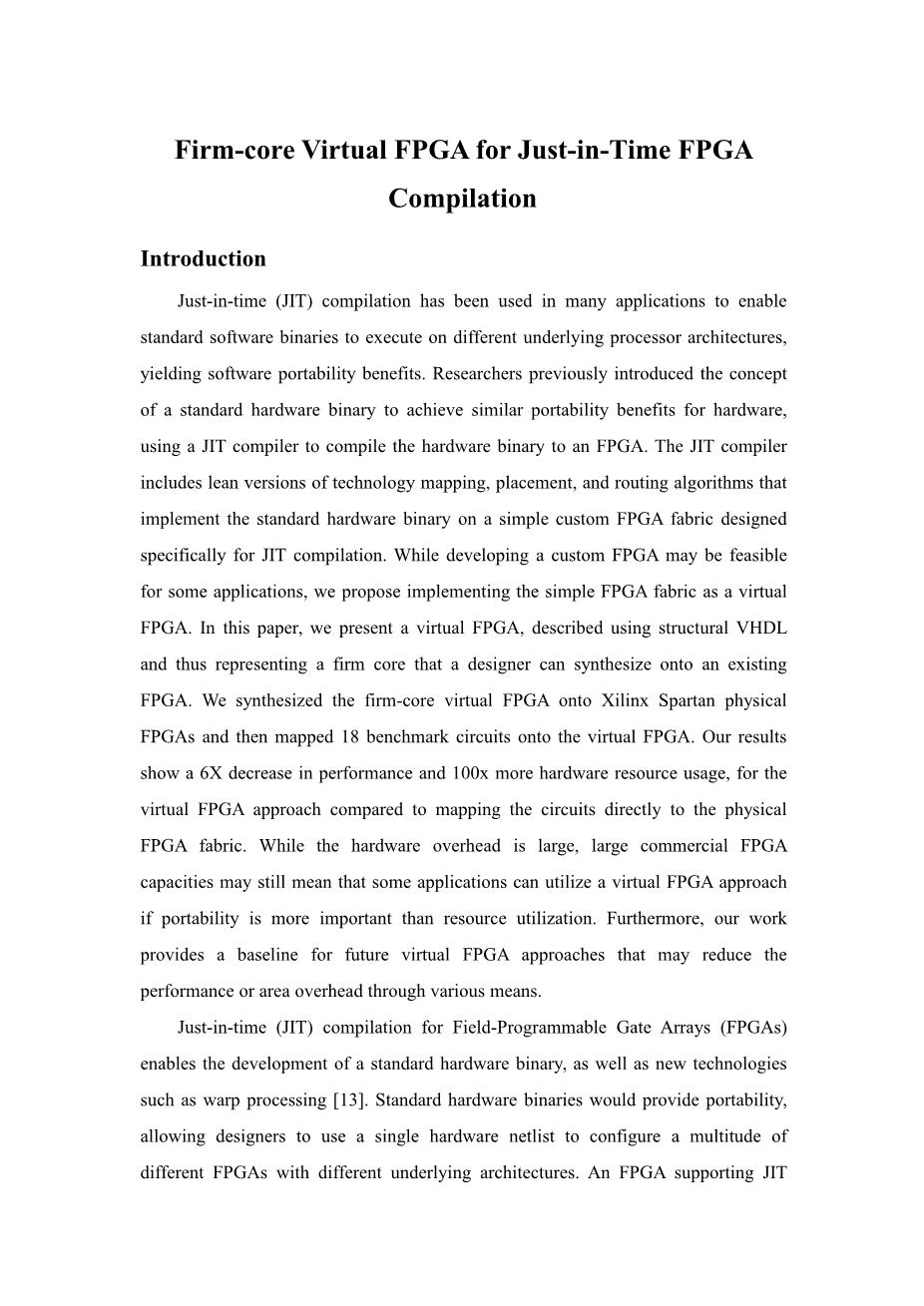

图1中:(a)SimpleFPGA可配置逻辑结构(b)可配置逻辑块(CLB)和(c)交换矩阵(SM)架构。

之前,研究人员开发了一套精简的JITFPGA编译工具,将标准硬件网表编译到

一个简单的自定义可配置的逻辑结构[10][11]。编译到一个FPGA是出了名的耗时的,然而,这在很大程度上是由于放置和路由。

JITFPGA编译器必须在精益处理资源上执行芯片,可能只是一个内存有限的小型32位嵌入式处理器,该处理器甚至可能是FPGA本身上的软处理器核心。因此,而不是针对商业可用的FPGA,这些研究人员开发了一个简单的FPGA织物专门为快速地点和路线,结合JIT编译工具,为了使他们的精益的开发工具,执行使用非常有限的内存资源和执行时间,同时产生良好的结果。如果我们可以扩展JIT编译方法来支持任何现有FPGA或未来FPGA产品的使用,我们就可以进一步增加JITFPGA编译的有用性。然而,一组支持如此广泛的FPGA的JIT编译工具将需要更多的内存资源和更长的执行时间,从而导致一组工具不再适合于精益芯片上执行。

或者,可以通过将结构映射到现有的FPGA来实现简单的自定义可配置逻辑结构,因为简单的结构实际上只是另一个电路,这意味着简单的结构将是一个“虚拟FPGA”。通过在JITFPGA编译器所目标的可配置逻辑结构和底层FPGA设备之间提供一层抽象,我们可以使用任何FPGA创建一个支持JIT编译的FPGA。然而,一个虚拟的FPGA也有几个缺点。通过添加一个抽象层,虚拟FPGA将需要一些额外的硬件资源来实现可配置逻辑结构中的组件。因此,与底层物理FPGA相比,虚拟FPGA的可用可配置逻辑的数量将会减少。此外,使用虚拟FPGA实现的硬件电路将具有更长的关键路径,因为通过一个信号必须传输的额外硬件资源。

此前,其他研究人员也研究了虚拟FPGA的实现。托雷森[14][15][16]和Sekanina[12]都提出开发类似的虚拟可配置逻辑结构,由粗粒度的功能单元组成。这些功能单元可以被编程来执行一些不同的逻辑操作,并为其结构提供路由机制。此外,这两项工作还集中于使其虚拟FPGA支持存储多个位流。

在执行过程中,虚拟结构提供了快速选择新的位流并重新编程到几种预先确定的配置之一的能力。Lagadec等[9]提出了一个系统,其中用户使用高级描述定义虚拟FPGA结构。在这种方法中,高级抽象将用于自动创建虚拟结构,以及针对新结构所需的放置和路由工具。虽然提出的系统可以支持FPGA中的任何粒度级别,但他们的工作集中于能够对两个8位输入执行加法、减法、最大或最小比较的粗粒度。论坛论坛[7]还提出了一个虚拟的FPGA系统。然而,在这项工作中,虚拟FPGA指的是一种使用操作系统支持在物理FPGA设备上交换FPGA配置的方法,很像虚拟内存系统。

在本文中,我们提出了一个基于[10]的可配置逻辑结构的虚拟FPGA结构。与以前的虚拟FPGA工作的主要区别是,我们的织物是一个细粒度的织物,很像现有的商业FPGA。为了确保我们可以使用任何可用的FPGA实现虚拟结构,我们开发了虚拟结构作为可合成的VHDL模型,使用低成本FPGA实现虚拟结构。使用我们的虚拟FPGA,我们可以开发一个支持标准硬件二进制文件的FPGA,也可以开发一个依赖于JIT编译的扭曲处理系统来动态地在硬件中重新实现关键的软件内核。在本文中,我们描述了一个简单的可配置的逻辑结构,我们的VHDL模型,以及评估我们的虚拟FPGA方法的性能和功率开销的实验。

即时FPGA编译

用于FPGA的JIT编译器由技术映射、放置和路由算法的精简版本组成。从标准的硬件二进制文件开始,JIT编译器执行技术映射,将硬件映射到可配置逻辑中的LUT上,并进一步将LUT打包到clb中。一旦映射,JIT编译器使用我们确定可配置逻辑中每个CLB的位置

贪婪的放置算法。放置算法试图将位置分配给clb,以减少电路的关键路径,同时确保电路可以被路由。最后,JIT编译器执行路由,在此期间确定用于连接clb在一起的实际线段。

实现芯片上执行所需的精益CAD工具并不简单。现有的FPGACAD工具能够实现。

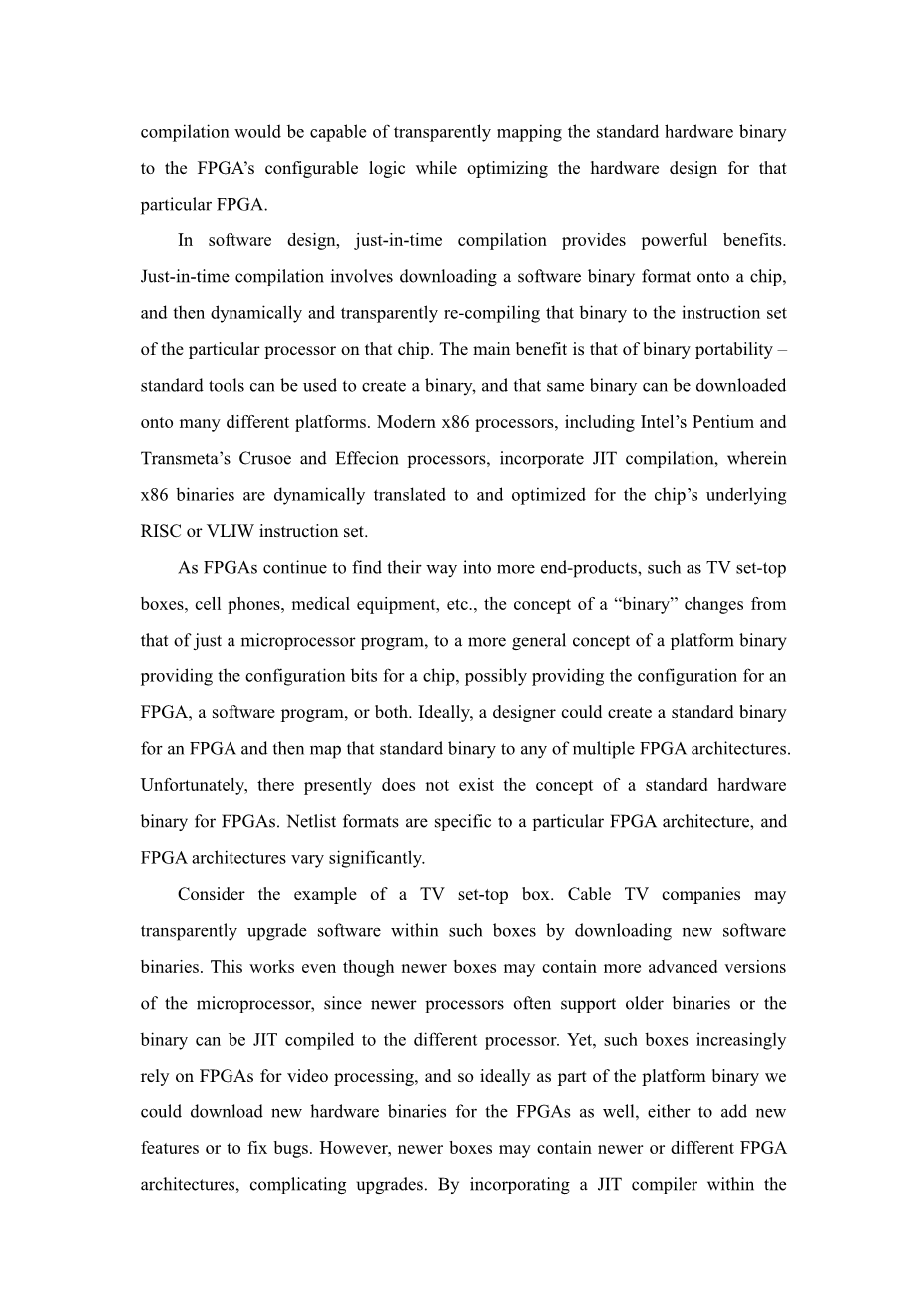

图2:虚拟可配置逻辑块,由4个3输入lut(2个3输入2输出lut组成。

生产高度优化的硬件电路。然而,这些工具的数据内存使用量非常大,通常超过100兆字节,执行时间很长,从几分钟到几小时不等。因此,[11]的研究人员设计了一个JIT编译器,专注于开发使用尽可能少的数据内存和快速执行时间快的精益算法。这些设计目标将固有地限制JIT编译器产生像桌面同行一样高度优化的设计的能力。然而,他们的片上CAD工具仍然能生产出可接受质量的硬件电路。

此外,研究人员还开发了一种简单的FPGA结构,专门设计用来为FPGA[10]开发一个精简的JIT编译器。图1(a)展示了它们的自定义可配置逻辑结构。FPGA由一组可配置逻辑块(CLB)组成,周围是交换矩阵(SM),用于CLB之间路由。每个CLB连接到一个开关矩阵,CLB的所有输入和输出都可以连接到它上。交换矩阵处理clb之间的路由,并可以在四个方向中的一个方向上将信号路由到相邻的SM或垂直间隔两行或水平间隔两列的SM。图1(b)显示了我们的可配置逻辑块架构。每个CLB由两个3输入2输出组成LUTs和四个人字拖可选地连接到每个四个输出。clb通过提供与相邻clb的直接连接以及CLB内的lut之间的连接,进一步支持携带链。最后,图1(c)显示了开关矩阵的体系结构。每个交换矩阵使用短信道连接相邻交换矩阵之间路由,长信道连接其他交换矩阵之间路由。通过交换矩阵布线只能将一条导线从给定通道的一侧连接到交换矩阵的另一侧的另一条导线。此外,每个短通道都与一个长通道配对,并可以在开关矩阵中连接在一起(表示为两个通道相交的圆圈),允许使用短连接和长连接路由网络。

虚拟FPGA

在开发虚拟FPGA时,我们确定了实现虚拟FPGA的两种可能的方法:

- 硬核虚拟FPGA:一种目标FPGA织物的结构性VHDL模型,可以使用任何合适的合成工具合成到任何物理FPGA设备上。

- 硬核虚拟FPGA:由特定FPGA设备的部分位流组成的定制实现,其中位流中的未编程位用于存储虚拟结构的配置。

与核心方法相比,公司核心的虚拟FPGA提供了许多优势。不仅VHDL模型可以被合成到任意数量的FPGAs设备上,而且设计者还可以使用VHDL模型进行仿真。此外,可以快速添加新特性并将体系结构更改合并到虚拟结构中,而不需要硬核虚拟FPGA中需要的任何耗时的修改。

或者,在硬核虚拟FPGA中,可以通过利用特定FPGA的底层物理组件和重复使用物理路由资源和可配置组件来实现虚拟结构。在这种方法中,用于配置物理FPGA的位流将由两个相互交织的数据流组成

元素:创建虚拟FPGA的固定部分配置和用于编程虚拟结构的行为的变量配置。虽然这种方法不能跨不同的FPGA设备(甚至是同一FPGA家族中的不同设备)进行移植,但硬核虚拟FPGA将比公司核心方法需要更少的开销和提供更好的性能。在[4]中,研究人员使用FPGA开发了一个大型的动态可编程的横杆开关。研究人员利用物理结构特性来实现开关结构,有效地实现了可编程的横杆开关。

虽然核心虚拟FPGA有很多优点,但我们开发虚拟结构的最初目标是提供一个非常灵活和便携的虚拟FPGA。因此,本文的工作重点是企业核心的虚拟FPGA设计。

组合逻辑块

图1中所示的可配置逻辑块包括两个3输入的2-ouptutLUTs、四个触发器和用于支持携带链和启用或绕过触发器的逻辑使用。此外,在一个典型的FPGA中,CLB还将包含用于存储clb配置的SRAM位,包括lut的内容。图2给出了可配置逻辑块的虚拟实现。我们将每个3输入2输出查找表表示为具有相同的3输入的两个3输入1输出查找。各个查找表使用一个8位移位寄存器来实现,它的输出连接到一个产生单位输出的8-1多路复用器。

图3:基于虚拟三态缓冲区的交换机矩阵:(a)整体交换机矩阵架构,(b)内部路由交换机,(c)可配置逻辑块(CLB)接口。

虚拟CLB将来自多路复用器的CLB的输出连接到使用触发器实现的CLB的顺序元素。触发器输出和LUT的输出连接到一个2对1的多路复用器,允许配置选择顺序输出的组合。此外,对LUT的最不重要的输入可以来自CLB的主输入c或f,或者来自相邻的CLB和LUT的输出。我们为每个lut使用两个2对1多路复用器实现这种可编程性。

我们可以通过移位虚拟流使用pdin输入连接到移位寄存器来存储CLB的配置。一个典型的FPGA将使用一个基于SRAM的移位寄存器来存储位流。然而,我们的虚拟FPGA使用顺序连接的触发器实现了移位寄存器。图2展示了配置移位寄存器,并演示了各种可配置的位是如何与虚拟CLB连接的。配置移位寄存器的最后一个触发器pdout的输出将通过虚拟FPGA连接到其他clb和交换矩阵,以创建用于编程结构的整个配置移位寄存器接口。

交换机矩阵

在传统的FPGA中,交换机矩阵通过可编程的互连来提供路由资源。可编程互连可以实现为连接两根导线的单通晶体管。此外,通过这种实现,连接在开关矩阵中的电线可以作为输入或输出。然而,虽然VHDL确实提供双向端口和信号,但如果不可能的话,使用双向信号开发虚拟交换矩阵是困难的这是不可能的,因为我们需要事先知道电路中的哪些元件将驱动输入和接收输出。相反,我们通过将虚拟交换矩阵的每根连接

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[604016],资料为PDF文档或Word文档,PDF文档可免费转换为Word