高速窄脉冲信号IP核的设计开题报告

2020-04-12 08:49:40

1. 研究目的与意义(文献综述)

1.1 研究目的及意义

现代电子技术的高速化、智能化以及多维化的快速发展给人们的生活带来了

极大的方便,随着半导体技术和集成工艺的崛起和飞速发展,各种新型电子系统蓬勃兴起,其中以计算机技术为代表的数字系统得到了越来越广泛的应用,通信与测试信号均呈现高速、高精度、复杂化、高度可编程的趋势。脉冲技术是伴随电子测试技术的发展而兴起,各种高性能脉冲发生器广泛应用于不同领域:在数字集成电路、高速系统和射频电路等测试中,需要频率范围极宽、频率分辨率高的具有可控能力的脉冲信号;窄脉冲在光谱学中也常用于驱动LED测量材料研究;窄脉冲激发电场目前正在用于诱导细胞凋亡来治疗癌症和其他疾病生物医学领域;在光纤传感领域中,高速脉冲信号的激光驱动电路是OTDR实现高分辨率的关键;此外,纳秒脉冲宽度和以下数量级窄脉冲通常用于超宽带无线通信中的数据通信。因此高速脉冲技术已经逐步成为许多电子系统技术发展和测试的关键技术。

在脉冲波形产生方面,最初的谐振电路与整形技术相结合的脉冲产生方法,由于脉冲重复频率分辨率低、频率范围窄,波形可编程能力较弱等缺陷已经极少应用于通用脉冲信号的产生。而利用数字技术的竞争冒险和波形合成技术产生的脉冲波可编程能力较弱,设计的脉冲发生电路只能应用于特定的系统,缺乏扩展能力。现场可编程逻辑门阵列FPGA(FieldProgrammable Gate Array)是一种可以编程的数字集成电路IC(Iintegrated Circuit),它包含了可配置的逻辑块、可配置的 I/O 模块和可编程互联资源这三个基本模块。其具有低成本、高度集成化、数据处理与运算的高速度、高性能以及灵活的接口方式等优势。为了满足通用脉冲技术的要求和扩展脉冲波发生器应用场合,本文结合FPGA丰富的逻辑资源,设计一个能产生可编程的高速脉冲信号发生器,使该脉冲波发生器能应用于多种应用场合,而不再局限于某个特定的系统。

1.2 国内外研究现状

从当前脉冲发生器研制方面看,许多国外知名企业如美国的Tektronix公司和Agilent公司等已经掌握了非常成熟的研制技术,而且其产品相当先进,在世界范围内都得到广泛运用。

在脉冲信号发生方面,安捷伦Agilent公司通过打造其强大的脉冲发生器家族阵容,涵盖了广泛的输出频率范围。目前,Agilent公司的脉冲/数据发生器家族包括有811O1 A, 81104A, 8111 OA,8113 OA, 81132A和81141A, 其输出的脉冲最高频率可以从80MHz, 165MHz到400MHz, 660MHz再到7 GHz,13.5GHz, 同时安捷伦Agilent公司和泰克Tektronix公司在极窄脉宽的发生技术方面也处于领先地位:安捷伦Agilent公司的81142A脉冲/数据发生器能够产生最小脉宽为35ps的脉冲;泰克Tektronix公司典型的DTG5334能输出最小脉宽达290ps的脉冲信号。

国内对于高速脉冲发生器的研究已经取得了长足的进步,但由于起步较晚和

技术不足等原因国内的脉冲发生器研制技术还不够成熟,目前处于领先地位的是电子科技大学和南通南峰电子公司。电子科技大学研制的脉冲数据发生器频率最高已经达到250MHz,输出数据率500Mb/s,且能够单端或差分输出;南峰电子的产品在脉冲重复频率上也达到了100MHz的水平,而其他公司的产品仍然偏低端。现阶段,由于国外的技术封锁和自身的起步相对较晚,国内在高速极窄脉冲合成的研究上还处于起步的阶段,还有很长的路要走。

2. 研究的基本内容与方案

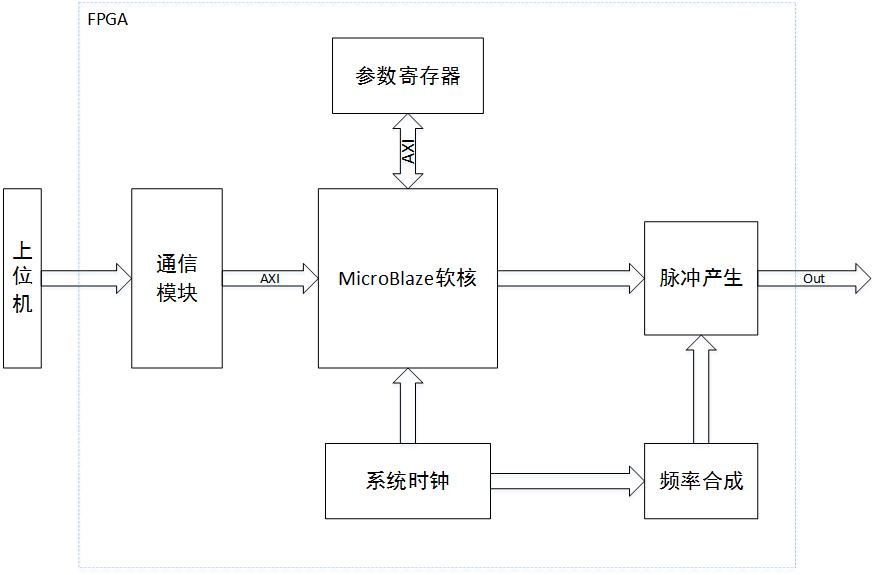

| 本文拟采用Xilinx Kintex 7 FPGA 评估板实现一个可以通过上位机软件实现脉冲信号频率与脉宽的任意调节高速窄脉冲发生器,并将核心的模块通过软核设计的方式封装成IP核,以便再开发利用时方便调用,而避免再次开发。 本设计利用Xilinx官方提供的开发软件vivado,使用Verilog语言完成高速窄脉冲IP核的设计。借助Xilinx官方提供的IP核搭建嵌入式系统平台,并编写上位机软件对IP核进行功能验证。 具体的设计分为三个部分:第一部分为高速窄脉冲产生模块设计,该部分利用FPGA丰富的逻辑门资源,以数字电路知识作为理论基础实现脉冲波产生。第二部分为嵌入式系统平台构建,完成FPGA与上位机的通信,实现上位机对脉冲波参数的调控。第三部分编写上位机测试软件,方便对脉冲的参数进行调控和对整个系统功能进行测试。主要包括以下模块:MicroBlaze软核控制模块、ethernet模块、串口通信模块、时钟产生模块、上位机、脉冲产生模块和参数寄存器。其中MicroBlaze模块是整个嵌入式平台的控制中心,协调各个模块的功能。通信模块包含ethernet模块和串口通信模块,主要完成上位机和FPGA之间通信,将要求的参数传递给FPGA,时钟产生模块为整个设计提供系统时钟,系统时钟通过频率合成模块后为脉冲产生模块提供原始波形。参数寄存器存放脉冲的频率和脉宽等参数,脉冲产生模块根据寄存器中的参数产生符合要求的脉冲。 图1 总体结构图 |

3. 研究计划与安排

| 第1-4周:查阅相关文献资料,明确研究内容,了解研究所需理论基础。确定方案,完成开题报告。 第5-6周:熟悉掌握基本理论,完成英文资料的翻译,熟悉开发环境。 第7-9周:实现各模块功能,并初步构成完整系统。 第10-12周:针对具体的实验数据,完成整个系统的仿真,实现功能;撰写论文初稿。 第13-16周:修改毕业论文。 第17周:论文答辩。 |

4. 参考文献(12篇以上)

| [1]ZHANG Hui-ying.Research about nanosecond pulse light source with LED-based and ap-plicationin spectroscopy [D]. Beijing: Beijing Jiaotong University, 2010. [2]徐文强,任勇峰,文丰. 基于FPGA的高速脉冲信号源的设计与实现[J]. 微计算机信息.2007,02:251-252 229. [3]CHOPINET L, ROLS M P. Nanosecond electric pulses: Amini-review of the present state of the art [J]. Bioelectrochemistry, 2014. [6]仵宗钦,刘鹏. 基于FPGA的高速脉冲位置调制激光通信系统设计[J]. 激光杂志.2015,08:120-123. [13]尹成群,田航,李永倩等. 布里渊传感系统中超高速方波脉冲源的设计[J].激光技术.2014,Vol38,No.5. [14]张志诚.高速极窄脉冲合成技术[D].电子科技大学.2013. [15] Yuan Wang, Yi Li, Yanqing Qiu, Pengwei Zhou, XinyongDong. Study of Narrow Pulse Driver Circuit with Adjustable Width andAmplitude[J]. 16th InternationalConference on Optical Communications and Networks.2017. [16]樊孝明,林基明等.超宽带极窄脉冲设计与产生[J].现代雷达.2006,Vol.28,No.3 [14]赵红梅,王园璞,崔光照.双非门结构皮秒级窄脉冲设计[J].电子器件.2015, Vol. 38 No. 3. [17]章 欣.基于FPGA的脉冲信号发生器设计[J].气象水文海洋仪器.2014. [18]付在明.高速脉冲波形合成关键技术研究[D].电子科技大学.2015. [19] I. Vegas, P. Antoranz, J.M. Miranda, F.J. Franco. Design of a variable width pulse generator feasible formanual or automatic control[J]. Nuclear Instruments and Methodsin Physics Research A.2017 [20] ZHU Yu, WANG Lian-ming. Design and Implementationof Nanosecond Pulse |