用于无线通信中的天线阵列的支持和使能电路外文翻译资料

2022-12-24 16:52:47

英语原文共 12 页,剩余内容已隐藏,支付完成后下载完整资料

用于无线通信中的天线阵列的支持和使能电路

本文对硅解决方案的低功耗和低成本的整合重点无线天线阵波束形成的四种结构概述。

由艾达S. Y. Poon,IEEE高级会员,IEEE学生会员,Mazhareddin Taghivand,

摘要:天线阵列已经被证明是一个很有前途的高速无线网络技术,并预计将在未来的无线通信系统中不可缺少的组成部分。本文提出了一种在结合不同的信号接收阵列的元素以及分裂的信号传输解决方案的重点不同于硅基阵列单元的电路技术观。它还审查电路技术来控制从/到每个数组元素的信号的相位和振幅,使得从这些阵列元素的信号可以结合和分裂的期望的方式,用于实现高数据速率的通信,以及干扰管理。

关键词:阵列天线;基带波束形成;笛卡尔矢量调制器;数字波束形成;加载线移相器;本地振荡器(LO)波束形成;罗路移相器;毫米波通信;相位采样矢量调制器;反射式移相器;射频(RF)波束形成;切换延迟移相器;无线局域网(WLAN)60 GHz通信;

- 介绍

无线通信超越视线始于1901,当Marconi得到了第一个无线电信号穿越大西洋。当电离层为地球的信号提供反射面时,信号跟随地球的曲率。在上世纪50年代中期,在对流层散射颗粒用于在甚高频(VHF)频段的远程通信。在过去的三年中,周围的群山和高层建筑的衍射有助于减少基站部署在蜂窝/个人通信服务(PCS)系统的超高频(UHF)频段。物理环境的散射性质的进一步利用天线阵列来提高数据速率的垂直贝尔实验室证明分层空时码(V-BLAST)系统[ 1 ],[ 2 ]在上世纪90年代。原型的多天线系统由贝尔实验室建立了散射源如墙壁和家具的能力令人印象深刻增加。V-BLAST成功率的多输入多输出(MIMO–增殖)使用超高频系统(SHF)带。在本世纪初,它被包含在无线局域网(WLAN)的标准,作为一个整体部件达到几100 MB /秒,领先的无晶圆厂半导体公司数据率的无线通信包括博通和高通Atheros公司[ 3 ] [ 4 ],[ 5 ]所开发的产品,包括高度集成的芯片解决方案。

今天,我们习惯于步行与我们的笔记本电脑和享受通过WiFi上网的便利,并检查电子邮件与我们的手机在路上。然而,仍然有相当大的差距在速度和安全水平之间的有线和无线连接。利用硅技术的缩放,FT和先进的互补金属氧化物半导体(CMOS––Fmax)和SiGe异质结双极晶体管(HBT)过程超过200 GHz。这使得低成本收发器在毫米波段。较高的载波频率允许使用更宽的频谱。例如,有7 GHz的无牌频谱在美国的60 GHz频段可用。multigigahertz谱允许千兆位与轻松的数据速率。这是对比目前的做法,填补了许多比特每赫兹频谱在WLAN和蜂窝系统。千兆位数据速率使无线和有线互联网接入骨干网无缝集成,它有可能彻底改变未来的互联网。初创公司和成熟公司包括SiBEAM [ 6 ],联发科,和IBM的[ 7 ],[ 8 ]正在开发高度集成的芯片解决方案。使用有源天线阵列的空间功率相结合,用于延长覆盖范围从几米的视线条件为10米的非视距条件。

由于天线阵列是在高数据速率的无线通信系统中不可缺少的组成部分,本文回顾了电路,使和支持天线阵列波束形成,强调以硅为基础的解决方案。

- 波束阵列

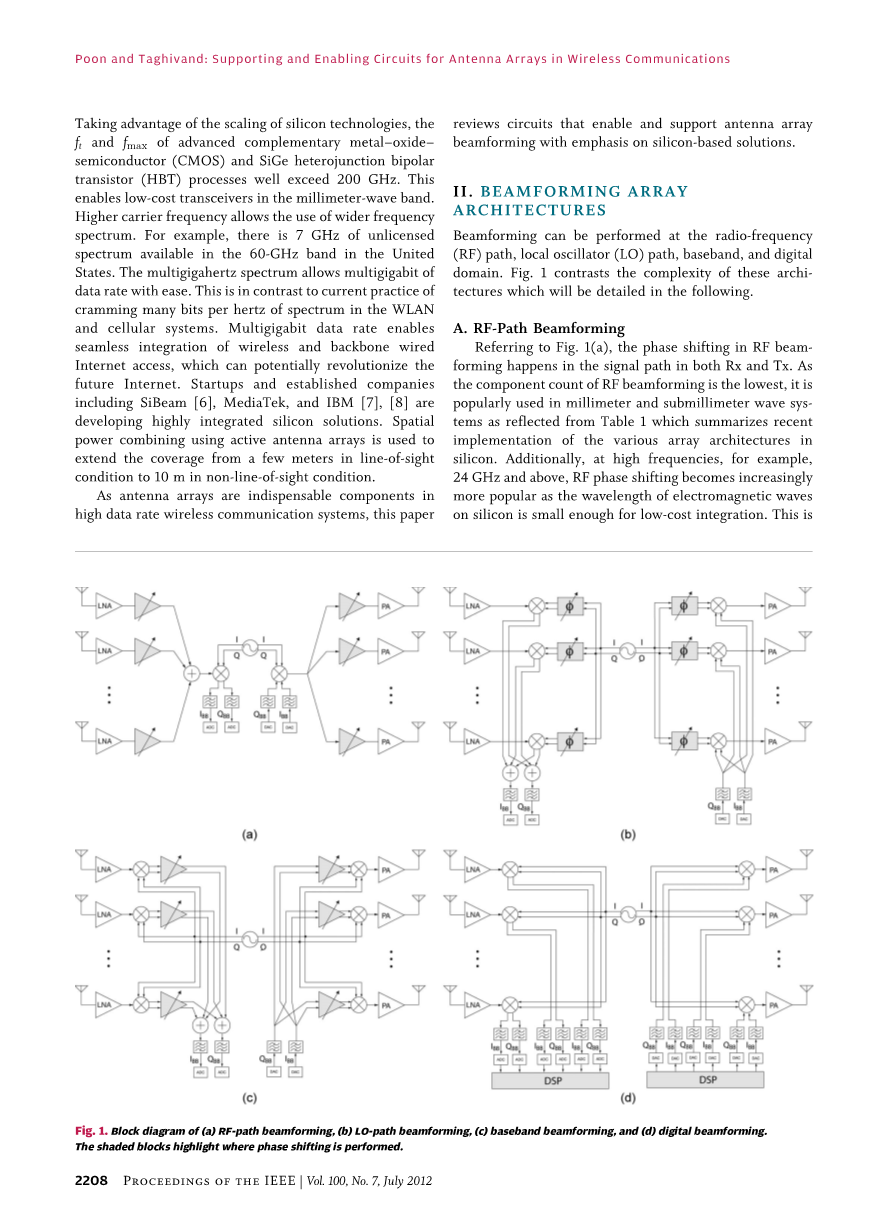

束形成可以在射频(RF)路径,本地振荡器(LO)路径,基带和数字域进行。图1对比这些系统组成,将在下面详细的复杂性。

- RF路径的波束形成

参考图1(a)、相位RF波束形成转移发生在RX和Tx.作为射频波束形成的元件数量的信号路径是最低的,这是普遍使用的从表1总结了各种阵列结构在最近实现硅反射毫米波、亚毫米波系统为。此外,在高频率,例如,24 GHz以上,RF相移变得越来越流行,因为硅上的电磁波的波长是足够小的低成本集成。这也是RF波束形成的一个主要优点,特别是对于大阵列系统。

在较低的频率,如700兆赫和5 GHz之间,它是难以设计真正的时间延迟或相移元件的波长是在厘米的顺序,这意味着它们的物理尺寸将是望而却步大。有源移相器在低千兆赫的频率可用,但他们可以在射频信号路径中引入噪声和非线性。

由于接收到的信号被添加在RF路径和混频器之前,因此仍然是不分解成I(相位)和Q(正交相位)的实际信号,有一个更大的风险的I / Q相位和振幅不平衡。多径和其他不必要的干扰将被空间滤波后的RF接收器路径组合后,并达到混频器之前。简单的LO生成和路由是另一个主要优点波束形成射频。混频器的数量也是最小的。

射频波束形成有一些缺点。噪声系数(NF)可以被降解由于在RF信号路径,这是总是有损相移。同时,射频移相器,通常不会获得高分辨率,潜在地限制了性能。

图一(a)RF路径波束形成,(b)LO路径波束形成,(c)基带波束形成和(d)数字波束形成框图。阴影块突出的地方进行移相。

表1最近四个波束形成阵列结构的硅实现

B.罗路的波束形成

参考图1(b),LO波束形成中的相移发生在LO分布网络中。在RX和Tx射频信号路径可以非常紧凑,可以提高NF的RX和TX宝tentially在相移在罗湖节省功率对系统信噪比(SNR)和增益的影响最小,在RX和Tx为噪声和线性度的要求是在罗在信号路径的同行更容易满足。使用正交电压控制振荡器(QVCO)[ 26 ]或环形振荡器[ 24 ]、[ 25 ]、精确的相移,在较宽的频带内可以实现的,这使得这种结构适合在低千兆赫的频率[ 21 ],[ 22 ]。

LO波束形成的一个主要问题是大的LO路由网络,它可以成为非常具有挑战性和功耗的数组大小增加。同时I/Q失衡的LO信号的混频器进行校准。为了校准在相位和振幅的I / Q不平衡,反馈环路从Tx到RX是必要的。这进一步复杂化的硅工艺,特别是大型阵列系统。

表2 N阵列系统的四种波束形成结构的优缺点

C.基带波束形成

参考图1(c),相位在基带波束移进行下变频后,在基带电路。不像射频波束形成在每个数组元素的相移,可以通过两个可变增益放大器(VGA),完成基带波束形成的相移为四VGA控制。基带波束要求每个单元混频器对LO,大型分销网络[ 30 ],并实施相位旋转和增益控制下变频后。I / Q失配可能是一个关键问题,因此仔细的I / Q校准是必要的。

这种架构的优点是,精细的相位分辨率,可以实现与更少的功率惩罚,作为相位旋转是在低频率的基带。因此,基带波束形成是一个很好的候选人时,需要一个精细相位分辨率。这也是一个用于低千兆赫的频率很好的候选人,为相移不需要被动元件。

D.数字波束形成

参考图1(d),数字波束形成中的移相是在数字信号处理(DSP)单元内的数字域中进行的。这个建筑是最适合低兆赫相控阵系统[ 3 ]–[ 5 ]、[ 31 ],在移相器是不容易设计和非常昂贵的集成。这种体系结构的优点是,相位旋转的工作是在数字域。因此,它简化了收发器的射频电路设计。

主要缺点是两个模数转换器(ADC)和数字模拟转换器(DAC)为每个数组元素需要。此外,I / Q不平衡可能是一个重大问题,在数字波束形成。除了相同的I/Q失衡问题作为基带波束形成,这个结构可能会受到不同的群延迟的问题在:I路和Q路基带链等他们经过独立的低通滤波器。这种架构尚未实施高千兆赫的频率,低功耗,高分辨率,快速实现非常具有挑战性的ADCs。它可能会改变在未来的CMOS得到更快和ADC的设计可以使数字波束形成与其他波束形成架构的竞争力。

最后,还有其他类型的波束形成建筑如交换巴特勒矩阵[ 35 ]束技术。波束图案是预定义的,因此,它是不太灵活比上述四波束形成架构。总之,选择哪种波束形成建筑的使用主要取决于工作频率,使用的硅技术节点,和数组元素的个数。表2总结了优点和缺点四波束形成结构。

三、相位和振幅控制电路

移相器是天线阵列中的整体元件。它们可以实现使用无源或有源器件,并使用集总或分布式元素。权衡的芯片面积,插入损耗,在相移范围损失变化,直流(DC)功耗、带宽和信号的线性度。在下面,我们将解释六种基本类型的移相器,以及它们的优点和缺点。类似的波束形成架构,有许多不同的变化,从这六个移相器,有多种方法相结合,以实现相移。

- 反射式移相器

反射式移相器(rtPS)由耦合器与它的两个端口连接到相同的反射力,如图2所示。可变相移调整反射加载实现,L和/或假设耦合器的特性阻抗Z0。对于特定的反射负载

相移是由反射系数的相位确定的

并由

因此,调谐C或L引入相移。这个相移范围取决于C的调谐范围和L.的耦合器和反射负载可以实现—利用无源或有源器件。系统支持比迪烟—离散相移。作为可调谐电感器不可用在大多数硅过程中,变容二极管通常用于反射负载。但变容二极管硅限制的范围调整电容。通常,变容二极管的电容可以由约2或以下因素。这限制了相移的范围。因此,电感增加,以增加相移通过调谐变容二极管电容的范围如图3所示(a)。谐振负载(RL)的损失可以通过将电容CT形成L-match减少阻抗变换网络,如图3所示(b)。zarei等人。[ 36 ],[ 40 ]实施谐振负载阻抗变换网络(RLT)在SiGe双极CMOS(BiCMOS)和CMOS。在CMOS

的实现,采用有源电感器实现实现低损耗。此外,3-dB 90同向

耦合器采用集总LC网络,如图4所示。即,实现由被动轮询耦合器和有源负载在2.4 GHz。

郑等。【37】另一方面,使用有源耦合器主动荷载。耦合器是由一个紧凑的三实现—晶体管有源环行器。有源谐振负载—输送用。表3的前两行比较它们的表演.基于有源耦合器的体系结构和有源负载实现更广泛的相移,招致损失少,占地面积少。基于体系结构在无源耦合器和有源负载,但是,消耗少得多的力量。移动到毫米波频率,吴等。[ 38 ]实现无源耦合器和无源负载等在24 GHz。耦合器是基于变压器的正交混合耦合器,并实现由多个金属层

CMOS。负载是一个类型的谐振负载,如图所示图3(c)。在[ 37 ]主动RTPS的比较混合型有源–被动RTPS在[ 36 ]和[ 40 ],被动RTPS遭受更多的损失。但自实施以来在24 GHz,被动等约占面积为活性等在2.4 GHz的相同。【39】采用粗线金属层耦合线实现耦合器,采用谐振式负载。60 GHz收发器由IBM和联发科[ 7 ],[ 8 ]是基于这种架构。损失的变化在相移设置有一个反相VGA采用的是[ 7 ]和[ 8 ]实现全360和细变增益补偿损失的种类。表3总结了RTPS近年来的发展及其性能。

图2反射式移相器

图3.在系统负载类型:(一)反射谐振负载(RL),(b)与阻抗变换谐振负载(RLT),和(c)型谐振负载(- RL)。

表3反射式移相器近期发展综述

B.负载线移相器

负载线移相器由可调谐串联和并联元件组成,如图5所示。它可以表明,对于一个给定的相移,电感和电容的值是由[ 42 ]

可调电感是不可用的,汉考克和rebeiz [ 42 ]近似的可调电感采用变容二极管系列固定电感器。相移范围将由MOS VA反应器是有限的调谐范围的确定。为了增加相移范围,多个变容二极管调谐LC网络串联连接。放大器有时插在变容二极管调谐LC网络之间,以补偿插入损耗[ 41 ]。在高频率,例如,60千兆赫,串联元件可以实现传输线[ 43 ]。表4总结了负载线移相器及其性能的最新发展。

表4负载线移相器近期发展综述

图6一个n位的切换延迟移相器

表5开关延迟移相器近期发展综述

C.开关延迟移相器

开关延迟移相器由单元电池级联而成,如图6所示。每个单元介绍了相移两种选择:TDN和t0dn。总的相移是由每个单元引入的相移之和。它本质上是一个数字移相器。在文献中实现不同的拓扑结构,用于实现延迟元件和开关。

LC网络通常用于实现每个单元单元中的延时单元。高通/低通和旁路/低通LC网络是流行的配置。在图7(a)所示的高通/低通配置中,高通滤波器路径和低通滤波器路径之间的相位产生第n位的相移。高通滤波器路径可以由旁路过滤路径取代,如图7(b)所示。高通/低通配置支持更广泛的带宽比其旁路对应。金属-绝缘体-金属(MIM)和金属超金属(MOM)电容器通常与螺旋电感一起用于实现LC网络。固态开关通常是通过一个PIN二极管或晶体管实现。

单元电池不必相同。不同细胞中使用[ 16 ]、[ 20 ]、[ 45 ]、[ 46 ]和[ 48 ]。通常,第n单元引入180 = 2n的相位移1。单元格的数目等于相位分辨率中的比特数。相同的细胞被用于[ 44 ]和[ 47 ]。分辨率变的log2 N个N是细胞的数量。表5总结了开关延迟移相器的最新发展及其性能。

D.笛卡尔矢量调制器

反射型,负载线和开关延迟移相器只控制信号的相位。这些移相器通常是有损和占据大的模具面积,由于使用许多无源器件。信号的振幅和相移的变化。VGA通常用来补偿这种变化。偶尔,这些VGA用于控制信号的幅度。也就是

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[28394],资料为PDF文档或Word文档,PDF文档可免费转换为Word