基于高效计算机建模的永磁同步电机驱动器的实时硬件在环仿真外文翻译资料

2022-10-30 10:45:52

英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

外文文献翻译一

基于高效计算机建模的永磁同步电机驱动器的实时硬件在环仿真

Antonio Griffo, Daniel Salt, Rafal Wrobel, David Drury

Department of Electrical and Electronic Engineering

University of Bristol

摘要:硬件在环测试允许在一个现实的环境中对一个物理系统进行控制器的开发和性能评价,被测系统在一个准确的实时仿真中被模拟。本文提出了一种计算效率高而准确的使用方法,用于永磁同步电机驱动系统的实时建模。所提出的方法基于同步参考帧,其中高次谐波的定子绕组分布和转子磁通代表着一个指定的顺序。也可从一组有限元计算参数提取的程序中知道。实时模型编码在基于FPGA的平台上,这种平台可以在市场获得。所提出的方法在永磁同步电机牵引应用设计中被验证。在实际电机上实时执行和实验测量的比较用来验证所提出的模型。

关键词:实时建模;硬件在环;同步电机;永磁同步电机

一.引言

在许多工业应用中,由于简化复杂控制算法的开发和测试阶段的可能性,互连工程系统的实时模拟获得了越来越多的研究兴趣。在实际的操作条件下,典型的许多工程系统的嵌入式控制器的测试如汽车能量转换系统设备,飞机或电力系统中的应用,需要在实验测试平台的成本和复杂性方面上的巨大努力。硬件在环(HIL)的概念已成为一种广泛使用的方法,使得控制器的性能在准确真实的时间模拟测试下被真实测试,而不需要访问复杂,昂贵的或不可用的硬件。实时数字仿真器已经商业化得到一些应用,包括电力系统建模,电力电子转换器和电机驱动器。早期的模拟器往往使用微处理器或数字信号处理器(DSP)往往成串排列为了提高模拟更多复杂系统所需的计算能力。最近的一个趋势是内在并行现场可编程门阵列(FPGA)的使用,它允许更精确的模拟快速瞬变的模拟,如那些相关的电磁暂态和开关特性的电力电子转换器。采样率在几百kHz到几MHz的范围内,需要准确地捕捉脉冲宽度调制(PWM)信号,如开关的开启和关闭时,功率电子转换器的PWM频率在几十千赫已越来越普遍。准确的电机驱动器的实时模拟还需要考虑高保真的机器模型,以捕捉现象往往被忽视的简化模型,如在机器的电流和转矩输出中的高阶谐波以及饱和效应。对永磁同步电机仿真中最常用的模型(PMSM)是基于经典的两轴式Park同步参考帧。然而,由此产生的dq模型是基于简化的假设,忽略了因非正弦绕组分布和转子磁场引起的饱和和高阶的空间谐波。其结果是,非正弦反电动势(EMF),高次谐波电流的定子电流以及周期性转矩脉动不能准确预测。

多相变量模型已被提出作为一个准确而有效的替代计算dq模型的方法。这些模型是基于相位可变电感,先利用有限元分析(FEA)计算,存储在大型查找表功能的转子位置角和定子电流。另外,插值样条的使用也被提出最近。相位变量模型已被用于在离线和实时模拟。大型三维查表用商用有限元软件用于存储预计算相电感。这种方法可能需要大量的FPGA实现资源的利用和可能增加的计算时间。本文提出了使用较少的计算繁重的方法的基础上的同步参考帧的方法,其中高次谐波的定子绕组分布和转子磁通是完全代表了一个指定的顺序。从一组FE计算提取参数的程序也有报道。实时模型编码在市售的基于FPGA平台上。该方法被验证在一个典型的永磁同步电机(IPM)设计的牵引应用上。在实际电机上离线模拟,实时执行和实验测量的比较已被用来验证所提出的建模。

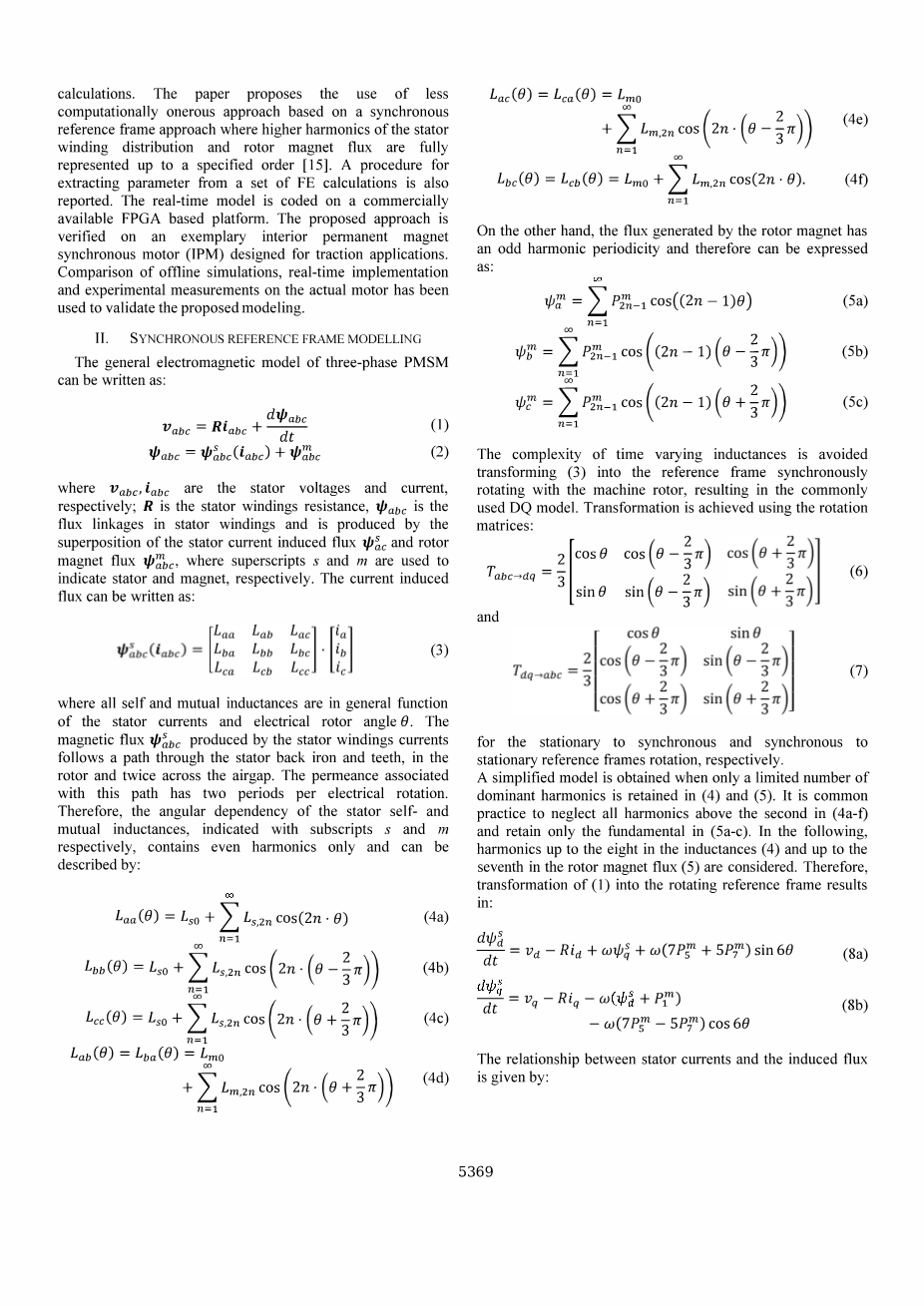

二.同步参考帧建模

三相永磁同步电动机的一般电磁模型可以写成:

Vabo iabe分别是定子电压和电流;R为定子绕组电阻,是定子绕组的磁链和通过叠加的定子电流引起的磁通产生,上标s和m分别表示定子和磁体。感应通量产生的电流可以写成:

所有的自感、互感都在定子电流和电机转子角一般功能内。由定子绕组电流产生的磁通量沿着如下的路径,通过定子铁芯和牙齿,到转子和两次穿过气隙。与此相关的路径的渗透每电旋转有两时期。因此,定子自感和互感的角度依赖性分别用下标S和M表示,含有偶次谐波,可以描述的:

另一方面,由转子磁铁产生的磁通具有奇谐波周期性,因此可以表示为:

时变电感的复杂性被避免转化为参考帧同步旋转的电机转子,导致常用dq模型。使用旋转矩阵实现变换:

一个简化的模型被获得,当只有有限数量的占主导地位的谐波被保留在(4)和(5)。常见的做法是忽略所有谐波以上第二(4a-f)和只保留基本在(Sa-c)。在下面,谐波达到8在电感(4)和高达第七的转子磁通(5)被认为。因此,(1)转换成旋转参考帧导致的结果

定子电流和感应磁通之间的关系

(9)中的电感是依赖转子角度,给出了:

中间代数计算获得的(8)-(10)因空间限制不报告,但值得注意的是,只有COS 6theta;,sin6theta;被保留,而较低的被取消。由于所实现的模型是电压驱动的,输出电流可以通过变换(9)计算。

三.模型参数的计算

A.参数计算程序

对于一个给定的永磁同步电机,在(10)-(12)中的电感可以从一组铁分析中鉴定。在定子绕组中通入预定的励磁电流,同时执行转子的全电旋转。一个特定在实际操作机器扫描当前所有可能的角度的选择,是为了选择定子电流 Ia =I,IB = -0.5I,IC = -0.5I,I所在的是电流的量级。在每个定子相的磁链可以在有限元分析计算和所预测的模型(2)比较,模型(2)中电流引起的通量(3)和磁通量与近似电感模型(4)和(5)评价,谐波限制在一个指定的顺序。电感和磁通量研究通过均方误差最小化之间的有限元计算的预测近似模型计算。最简单的形式可以被表示为:

一些确定性或随机优化算法可以应用于解决最小化问题(4)。在施耐德单纯形方法已用于以下应用。

B.基于有限元参数计算方法的应用

已应用于永磁同步电机7.5kW截面、绕组排列和PM的定位,如图1所示

电机是磁通聚焦轮辐式磁铁,用于牵引应用开发18-slots六杆机。有限元分析已经与电流范围从0到70A以5A的步骤进行,而转子已通过360电度以3deg步骤在旋转。

分析中忽略了端部绕组的影响。图2a显示有限元相磁计算结果,而图2b显示了近似的磁链用模型(2)-(5)获得,带有最大电感谐波限制在8和磁通量模拟到第七次谐波。如图2c所示的错误,被限制在plusmn;10%和小于1%,plusmn;90电度对应的Q轴,因此区域是电机更容易在最大转矩区对单位电流操作。图3显示了磁由模型(3)-(4)的定子绕组电流产生的磁链,而图4显示了转子磁链,由模型(5)计算得到的转子磁场。自感和互感到八阶当被计算提出的优化过程如图5所示。对于该模型的实际执行的目的,提取的电感都配有一个二阶多项式插值:

系数A,B,C的多项式插值在Tab.1。类似于图6表示出的永磁磁通分量高达第七阶由建议的优化过程和插值多项式,其系数在Tab给出在Tab.

四.实时模型的实现

该模型已经实现在对数据的实时采集和NI cRIO 9118的控制平台上。代码在一个8MHz时钟周期内运行在基于Xilinx Virtex5 LX 11 0设备FPGA底盘。因此该模型计算的延迟是125ns。PWM栅极驱动数字输入以4.44mhz被采样。一个12位数字总线仿真旋转变压器数字(R2D)150khz输出更新速率。输出电流与NI 9263数字到模拟转换器在100kHz速率产生。一个标准的磁场定向控制器中实现了基于FPGA平台的sbrio-9606 Spartan-6 LX45如图7所示。驱动控制器与实时仿真与适当的12bit为R2D接口的数字输入接口的cRIO运行,电流测量3路模拟输入,和栅极驱动控制6路数字量输出。PWM频率设定在12KHz。

五.验证

所提出的模型和它的实时实现已经验证了对实际电机的驱动。用于安装在测功机试验台所提出的建模的永磁同步电动机如图8所示。电机被驱动通过自定义基于英飞凌f400r06器件IGBT逆变器。9和10显示结果的实时模拟输出电流的比较和基于实际驱动系统的电流测量,电机运行在一个恒定的转速为500rpm,42arms电流。

六.结论

本文介绍了一种基于同步参考框架下使用永磁同步电机的仿真建模方法。模型与常用dq模型具有相同的计算效率,而且能够捕捉高阶效应由于磁通与绕组空间谐波以及饱和度。从有限元分析中所提出的建模方法所需的参数提取的过程也被描述。

该模型适用于FPGA的实施,基于实时仿真器用于电机驱动控制器的HIL式的发展。该应用程序的一个例子被给出,该模型实现在市售的实时数据采集和控制平台上。对实际的电机驱动系统模型的准确性也进行了验证。

外文文献翻译二

DSP Builder高级模块

DSP Builder高级模块由几个Simulink库,让你轻松快速实现DSP设计。DSP Builder是一个高层次的合成技术,优化高层次、不计时表为低电平,流水线硬件为你的目标和期望reg;Altera FPGA设备的时钟速率。DSP Builder实现硬件VHDL或Verilog HDL与脚本结合Quartusreg;Prime软件和Modelsim仿真器。您可以创建设计不需要详细的设备知识和生成,运行在各种不同的硬件架构,FPGA的家庭设计。DSP生成器允许您手动描述算法函数并应用基于规则的方法生成硬件优化代码。先进的模块特别适合流算法具有连续数据流和偶尔的控制。例如,包括长过滤链的RF卡设计。指定所需的时钟频率后,目标设备的家庭,通道数,和其他顶级设计约束,DSP Builder管道生成的RTL实现定时关闭。通过分析系统水平的制约,DSP Builder还优化了折叠平衡延迟与资源,无需人工RTL编辑。DSP Builder高级模块包括它自己的时序驱动的IP模块,可以产生高绩效执行‐FIR,中投和NCO模型。

1 DSP Builder高级模块特点1-1 2页。DSP Builder高级模块库3页1-2。DSP Builder设计先进的模块结构在1-3页组织你的DSP Builder设计成层次仿真子系统。每个顶层设计必须包含一个信号块和一个控制块,设备块必须在合成顶层设计中。

DSP Builder高级模块特点bull;自动流水线来实现定时关闭bull;自动折叠bull;容易比较不同设备的家庭bull;高性能浮点设计bull;基于向导的界面的目标(在循环系统)的配置,生成并运行硬件验证系统。

DSP Builder设计先进的模块结构

组织你的DSP Builder设计成层次仿真子系统。每个顶层设计必须包含一个信号块和一个控制块,设备块必须在合成顶层设计中。注:DSP生成器设计只能有一个综合顶层设计,它可以包含许多子系统(原始和IP块),以帮助组织您的设计。任何原始块必须位于原始子系统层次,任何IP块必须是原始子系统层次结构之外。

一个DSP Builder高级模块的顶层设计包括:bull;仿真测试平台,提供设计输入可以让你分析的输入和输出bull;顶级配置块bull;可选内存接口规范和刺激块。bull;外部存储器块配置一个外部存储器接口bull;busstimulus Avalon接口和BusStimuliusFileReader刺激在模拟bull;编辑参数块作为一种快捷方式打开脚本setup_ lt;模型名称gt;块。M编辑。顶层设计必须有一个信号:bull;块指定总线时钟和系统时钟bull;控制块来指定输出目录和顶层RTL阈值参数

注意:每个DSP Builder设计必须控制模块和信号模块,允许你模拟或编译你的设计。不要将设备块置于顶层设计中。DSP Builder的传播数据从测试类型合成的顶层设计。

可综合的顶层设计,顶层设计是一个综合仿真子系统包含设备块,这套家庭的一部分,和速度等级的目标。可综合的顶层设计,在顶层生成硬件文件。可综合的顶层设计,包括层次结构的子系统,包括原始进一步水平。注意:仅在预定原始子系统内使用原始块。或者,你可以有更多的局部阈值块覆盖阈值设置定义的层次越高。

原始子系统原始子系统是用于原语和IP库块的预定域。一个原始的子系统必须具备:bull;一synthesisinfo块,合成风格设定计划,使DSP Builder可以重新分配管道和记忆优化达到预期的时钟频率。bull;边界块划定原始子系统:bull;信道(信道的输入),bull;channelout(信道的输出),bull;GPIn(通用输入)bull;gpout(通用输出)。DSP Builder的同步,通过相同的边界块连接。利用系统接口模块划定域的边界内的一个子系统。用SampleDelay块指定数据流的相对样本偏移:不是流水。在这些边界块DSP生成器优化的实施您指定的示意图。DSP生成器插入流水线寄存器,以达到指定的系统时钟速率。当DSP Builder插入流水线寄存器,它增加了等效延迟的并行信号,需要保持同步,使DSP建设者安排他们在一起。DSP Builder的时间表的信号,经过相同的输入边界块(频道或gpin)在同一时间点开始;信号经过同样的输出边界块(channelout或gpout)在同一时间点完成。DSP Builder添加任何流水线延迟,您添加到通过设计信号实现削减和平衡。DSP Builder采用校正的仿真在边界块来解释这种延迟在HDL生成。原始子系统作为一个整体保持周期精确。可以在包含原始块的原始子系统中指定进一步层次结构,但没有进一步的原始边界块或IP块

Convert

转换块执行输入的类型转换,并输出新的数据类型。如果输出数据类型小于输入,则可以选择性地执行截断、偏置或无偏舍入。LSB(最低有效位)必须在输入类型位的宽度值。

确定块如何设置输出数据类型:通过内部规则继承:整数和小数位数是输入数据类型位数的最大值。bull;通过反向投影继承:该块驱动器的下行块决定输出数据类型。如果驱动块不传播数据类型的驱动程序,你必须使用一个Simuli

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[138395],资料为PDF文档或Word文档,PDF文档可免费转换为Word