高开关频率DC/AC逆变器的基于FPGA的SPWM发生器的开发外文翻译资料

2022-09-06 11:16:48

英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

高开关频率DC/AC逆变器的基于FPGA的SPWM发生器的开发

Matina Lakka,Eftichios Koutroulis,IEEE会员,和Apostolos Dollas,IEEE高级会员

摘 要:

正弦波脉冲宽度调制(SPWM)的数字化发生器已经相比于基于模拟电路的发生器占了优势地位。在本文中提出了一个基于FPGA的SPWM发生器,它能够工作在高达1 MHz的开关频率(需要FPGA工作在100-160MHz),因此它能够满足现代单相DC / AC功率转换器的高开关频率要求。所提出的设计适用于一部分中型的FPGA,因此,可以整合于一些较大型设计中去。此外,它具有灵活的体系结构,可以适用到各种单相DC / AC逆变器的应用中去。由布局仿真和实验结果确认,相比于过去,本文提出的SPWM发生器呈现出更高的开关频率,更低的功耗,并产生所需的更高准确性的SPWM波形。

索引词:DC / AC逆变器;现场可编程门阵列(FPGA);高频率;正弦脉宽调制(SPWM)

一、导论

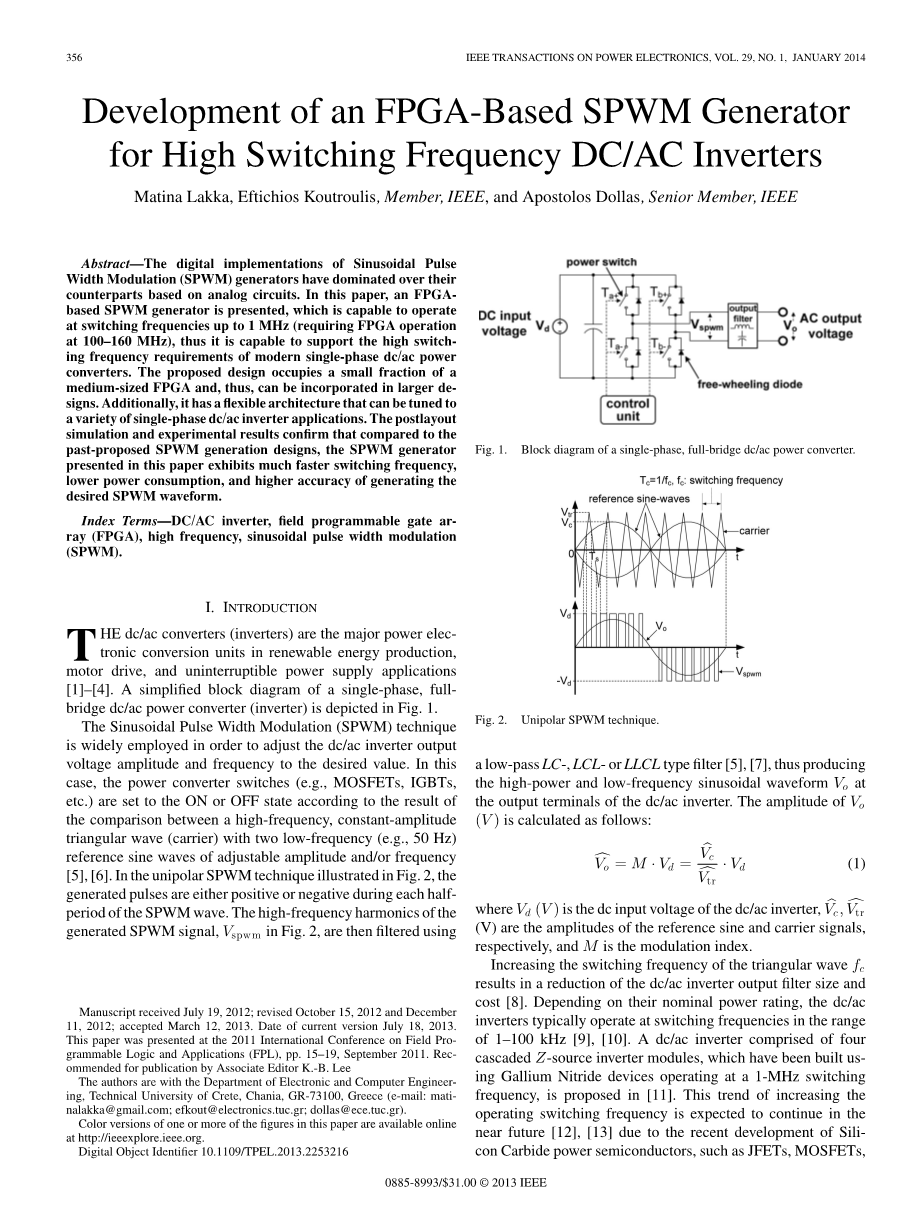

DC/AC转换器(逆变器)是在可再生能源生产,马达驱动器和不间断电源中应用的主要电力电子转换单元[1] - [4]。在图1中描绘了一个单相的简化框图,全桥DC/AC功率变换器(逆变器)。

正弦脉宽调制(SPWM)技术被广泛地应用以便调节所述DC / AC逆变器输出电压的振幅和频率为所需的值。在这种情况下,电力转换器的开关(例如,晶体管,IGBT的等),根据一个高频率,恒定振幅三角波(载波)与两个低频率(例如50Hz)可调节幅度或频率的参考正弦波之间比较的结果设置为ON或OFF状态,[5],[6]。在图2中所示的单极SPWM技术中,该装置产生的脉冲是正弦脉宽调制波每一个周期中或正或负。图2中 中SPWM波的高频谐波,经

收稿于2012年7月19日;修订于2012年10月15日和2012年12月11日;2013年三月12日被接收。当前版本的日期2013年7月18日。本文发表在现场可编程逻辑和应用程序的2011年国际会议(FPL),第15-19页,2011年9月。由副主编出版K.-B.Lee推荐。

作者是电子和计算机工程师部荷兰国际集团,克里特岛干尼亚科技大学,GR-73100,希腊(电子邮件:mati-nalakka@gmail.com; efkout@electronics.tuc.gr;dollas@ece.tuc.gr)。

本文多张图形中的多色版本可于http://ieeexplore.ieee.org在线阅读。数字对象标识:10.1109/ TPEL.2013.2253216

图 1 单相全桥DC / AC功率变换器的框图

图 2 单极性SPWM技术

一个低通LC-,LCL-或整箱型滤波器[5],[7] 滤波后使用。从而在DC / AC变换器的输出端子产生高功率和低频率的正弦波波形。的振幅(V)的计算公式如下:

其中,(V)是DC/AC变换器的直流输入电压,,(V),分别是基准正弦波和载波信号的幅度,M是调制指数。

增加三角波的的开关频率以减少的DC/AC逆变器输出滤波器的大小和成本[8]。取决于它们的额定功率,该DC/AC逆变器常在在该范围内即1-100kHz的开关频率上工作[9],[10]。DC/AC逆变器由四级联Z源逆变器模块组成,其中已经使用了内置频率在1 MHz的开关操作氮化镓器件,在[11]提出。操作的开关频率有继续增加的这一趋势,[12],[13]。近期由于碳化硅功率半导体,如JFET的,MOSFET和肖特基二极管[14] - [18]的发展,它能够在操作在低功率损耗的

图 3 在过去提出SPWM发生器的设计方法中正弦波数字化表示:(a)在

最低点采样(b)在最低点和载波的峰都在最低点采样。

高达3MHz开关频率下[19]。因此,由于该半导体技术的应用使开关频率的与常规DC/AC逆变器的比较起来增加了十倍[20]。

数字化SPWM发生器的实现使得它相比于基于模拟电路的发生器占了优势地位,因为它们提供更高的抗噪性和更低的电压和温度变化的易感性[21] 。通常,微控制器,数字信号处理器(DSP)或现场可编程门阵列(FPGA)被用于SPWM的生成单元和DC/AC逆变器控制算法的执行(例如,输出电压调节,模糊逻辑,马达速度控制等)[22]。控制系统和SPWM子系统在同一芯片中的一体化具有减少设计复杂性和系统总成本[23],[24]的优点。然而,微控制器[25]的和基于DSP的[26],[27]SPWM发生器单位实现发展至今在低开关频率级(即,1-10 kHz)下工作。如在[28]所讨论的,微处理器的运算速度和DSP的应用使得一个更高的切换频率上限可以使用基于软件的SPWM生成技术来达到。

利用FPGA的DC/AC逆变器控制逻辑的发展在过去几年已经很广泛,因为它们被认为是一个功能强大的和具有成本效益的解决方案[29]。相比于微控制器和DSP的集成电路,FPGA在改变的情况下具有灵活性的优点,以及由于它们能够整合数字硬件高速和并行处理功能[30] - [35]使得该DC / AC逆变器控制算法执行时间减少。

在介绍了基于FPGA的SPWM单元[21],[24],[36] - [41],三角波应用于上下计数器形式。根据该应用,基准正弦波以采样频率(定期取样脉冲宽度调制(PWM))在相应的载波的某一时刻只对最低点的[见图3(a)],或只对峰(对称调制)采样,或两者在最低点和载波的峰[不对称调制,图3(b)〕都采样。相应的样本以一个查找表(LUT)数字格式存储在FPGA中的内部存储器。 PWM控制信号由比较正弦和载波数字信号的相应值来产生。使用这些技术,SPWM在1.157-20kHZ范围的频率已经实现。相同的设计方法已在[23]被应用于基于所述OpenRISC 1200的32位的RISC处理器内核的SPWM信号发生SoC的发展上。

为了SPWM发生器存储器的减少要求,正弦波是在[42]使用基于FPGA实现坐标旋转数字算法(CORDIC)产生的。有一个5 kHz的开关频率已在这种情况下实现。虽然这个应用不需要使用一个硬件乘法器的,但是它相对于基于LUT的SPWM单元特征在较低的速度。所述CORDIC算法也已[43]应用在的集成电路的发展执行中,即采用0.18微米CMOS工艺的5 kHz的SPWM波发生器。

在[44]中,LUT被用来存储基准正弦波对应于三角波峰值和最低点的时刻的的数值。每个脉冲的宽度使用基于三角形ABC的相似的方程计算,ADF在图3(b)中描绘。这种设计方法已在1kHz开关频率的情况下进行验证。类似方法也被在[45]中提出。

在[46],SPWM脉冲串是通过比较正弦和三角信号经直接数字合成(DDS)技术产生的。该比较是使用高速模拟比较器进行。该DDS方法,可以在[47]用于采用0.35微米CMOS技术的PWM发生器数字芯片的发展。该芯片的最大时钟频率为50MHz。在[48],SPWM的单元由DSP芯片完成了的包含的各脉冲的宽度SPWM波的计算,通过与并行端口通信基于FPGA的单元产生SPWM控制信号。

在[28]提出的定期采样PWM技术,[49],以减少的计算时间在所需的量为目标,为了便于更高开关频率在线和实时的产生。在该技术中,脉冲宽度是计算一次,并使用SPWM波脉冲N个连续的开关边缘。然后,将基准正弦波的一个新的样本获取。因此,采样频率以整数因子N减少,有以下与相应的载频关系:

因此,产生完整的PWM波形所需要的运算的数目在传统的SPWM生成方法少N倍。

以前提出的SPWM的一个共同的缺点是先前所述的发生器,它们被设计在低开关频率(1-20kHz)来操作,而在较高的开关频率的操作尚未探索。在本文中,基于FPGA的SPWM发生器提出能使开关频率高达1 MHz;因此,它能够支持现代的单相的直流/交流电源转换器的高开关频率要求。相比以往提出的SPWM发生器,在所提出的架构中,两者基准正弦波和三角波的值被存储在FPGA器件RAM块(BRAMs)

图 4 所提出的SPWM产生单元的结构

以便利用其一个时钟周期的存取时间,从而提供了高得多的开关频率。提出的设计表现出灵活的特点,使SPWM开关的变化频率和调制指数在内部或外部。所提出的SPWM单元已经在一个单一的芯片实现以降低复杂性,成本,和所述DC/AC逆变器控制部的开发时间。

所提出的基于FPGA的PWM发生器的结构在第二部分进行分析,仿真和实验结果在第三节介绍。最后,本文提出了FPGA发生器与过去提出的系统其性能相比,以及相应的结果是在第四节进行分析。

二、提出的SPWM发生器

所提出的SPWM生成器的结构在图4中展示。系统输入是输出SPWM波在单精度浮点数字范围从0到1的调制指数M,“时钟”和“复位”信号也一样。

所提出的系统的体系结构已被使用内置8位定点运算,它由五个子系统来实现SPWM生成算法。正弦波的值数学上的范围[-1,1]中,已应用在所提出的架构中,以[0,255]等同的范围与对应于零点到“128”的离散值

A:时钟发生器子系统

“时钟发生器”子系统作为FPGA的输入时钟,并产生为所提出的SPWM发生器的数字电路使用一个新的时钟信号,使得所希望的SPWM开关频率能通过设计师/用户指定时产生。二态有限状态机(FSM)最初是用于设置输入时钟频率至/2,然后一个数字时钟管理模块适应这个频率到所需的值。超高速集成电路硬件描述语言(VHDL)的DCM模块的代码中于图 5所示。FSM保持对每个不同的开关频率不变,而只有操作参数“CLKFX_MULTIPLY”,并且将DCM的“CLKFX_DIVIDE” 模块根据SPWM输出波形的开关频率的要求改变。因此,所

图 5 在“时钟发生器”子系统DCM模块的 VHDL代码。

提出SPWM发生器是柔性的,以适应于由设计师/用户指定的任何操作开关频率的系统。

B.调制指数子系统

“调制指数”子系统用于转换为浮点调制指数M,这是在所提出的SPWM生成系统输入转换(Misin;[0,1])在定点运算对应的值。根据以下方程M的值被转换成一个新的浮点值:

其中n是体系结构的数字字长度。

增加n的值使控制生成SPWM波,分辨率更高的调制指数,但也导致在FPGA器件资源的更高的要求。然后所产生的浮点值被转换成一个定点值范围从0到255,经由浮动到固定点转换单元,由此产生的“调制指数”的“索引”输出在图4中所描绘子系统中。

C.正弦载波子系统

该“正弦载波”子系统包括控制单元,2BRAMs,其中包含正弦和三角(即载)波的样品和两个多路复用,它们产生两个恒定振幅的用于SPWM输出信号的产生的参考正弦波。正弦波和载波的BRAMs作为LUT操作。无论是正弦和三角波被采样和量化与相同的采样频率用MATLAB(例如 =4,8MHz等)。为了最大限度地减少FPGA资源的利用率,恒定振幅正弦波周期(时间间隔期间0-pi;/ 2,)的第

图 6 控制单元的FSM中所提出的PWM发生器:(一)流程图

在条件语句和(b)的伪代码

一季的唯一值存储在相应的BRAM里,而正弦波的值在pi;/2-2pi;期间由镜像和反相值来计算。载体的BRAM包含基准三角波的一个完整的周期的值。两个存储器的连续地址(“正弦地址”和“载体地址,”分别在图4)由控制单元在每个时钟周期都产生。该控制单元还产生一“标记”信号,它负责参考正弦波周期(pi;- 2pi;)期间正弦波的值的检索。如前面分析,等幅正弦波的BRAM扫描上下四次,由于该存储器仅包含正弦波周期的第一季度的值。该FSM产生正弦的地址和载体内存指针,“sineAddr”和“carAddr”分别是在图6(a)所示。这个FSM的第一状态(即,“状态0”)包含存储器的所有可能的条件地址指针,伪代码所示在图6(b)。“标志”信号的值确定用于检索存储在所述基准正弦波的BRAM存储器中的数据进行连续存取的方向是向上或向下。当“标记”设置为0时,多路转换器“MUX1”输入从恒定振幅正弦存储器读出的数据(“正弦数据”图4)。否则,“MUX1”输出对应于第二半周期的值(即pi;-2pi;期间)恒幅正弦波(参数“ys”图4)。

由“正弦载体子系统”的处理单元产生的通过变换存储在正弦存储器里的正值到相应的负值,根据下列等式:

其中x是存储正弦波BRAM中的正值。

图4中多路复用“MUX2”是用于生产第二恒定振幅基准正弦波,它与上述分析所述一个相比有180◦相位差。

D.振幅可调正弦子系统

“可调幅度正弦”子系统用作输入“正弦载波”子系统产生的恒定幅度的参考正弦值,并根据该值的调制指数M生成一个振幅可调的正弦数字信号,这是提出的SPWM生成系统的一个输入。的值的范围是0–255并计算如下:

其中y是恒定振幅基准正弦波的值,Index是“调制指数”子系统的输出,在第Ⅱ-B中所述。

E.比较子系统

在“比较”子系统实现高频等幅三角波(载体)与两个低频基准正弦波之间的比较,使用两个比较器(在图4“COMP”)。控制信号Ta ,Ta-,Tb和单相DC / AC逆变电源的Tb-开关在图1所示。 1从的输出生成此子系统的相应比较器,从而形成在DC / AC变换器的SPWM波(图1和图2中)输出端子。比较器中的“比较”子系统的输出(即,控制信号Ta 和Tb )等同于在部分中描述的“可调节的幅度正弦”子系统的相应的

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[146929],资料为PDF文档或Word文档,PDF文档可免费转换为Word