基于8051微控制器核心的单芯片语音识别系统外文翻译资料

2022-12-17 14:45:00

英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

毕业论文(翻译)

题 目 基于8051微控制器核心的单芯片语音识别系统

原 题 Single-Chip Speech Recognition System Based On 8051 Microcontroller Core

基于8051微控制器核心的单芯片语音识别系统

石渊源、刘佳、刘润生

清华大学电子工程系,100084,中国北京

- mail: shiyyQ hannah.ee.tsinghua.edu.cn

摘要:本文介绍了一种单芯片语音识别系统。它包含了提示、播放、扬声器等相关语音识别的语音功能,适用于玩具、游戏、消费类电子产品、办公设备等语音激活系统。该芯片是基于SOC(片上系统)理念并且嵌入了一个8位的MCU,RAM,ROM,ADC / DAC,PWM以及I / O端口和其他外围电路。包括控制/通信、语音编码和语音识别算法的软件模块,这种软件模块在8051兼容的微控制器核心中实现,从而使芯片的成本极低。语音识别采用模板匹配技术。它可识别多达20个短语,平均用时1秒,识别精度达到95%以上,背景信噪比高于10 dB。语音编码使用连续可变斜率增量调制(CVSD)算法,比特率为16kbits/s。

1、介绍

随着语音压缩/解压缩和语音识别的发展和成熟,语音正在成为人机界面的重要形式。该语音接口越来越多地用于办公自动化、工厂自动化和家庭自动化设备。到目前为止,大多数这些系统都是大规模的。现在正在提出将它们用于语音数据存储和传输的感知语音编码方法,或者能够给出合成的高质量机器的方案。并且所涉及的语音识别需要依靠一些连续大词汇量语音识别的系统,要求其在响应自然、流畅的人类语音时,能获得高水平的识别准确度,因此这些系统具有优异的性能。同时,它们很复杂,只能在计算机平台上使用。但是,在仅需要简单的机器提示和识别的区域中,例如玩具,游戏,消费电子产品等中的应用,具有提示,识别和回放能力的低成本系统是优选的。此外,如果考虑功耗,尺寸,成本,集成度和可靠性的优点,实现上述语音功能的单芯片语音识别系统是最佳选择并且可以广泛应用。

作为人机界面,语音识别系统应提供相互通信功能。为方便人们使用,预计能够“说出”一些提示来指导识别过程,并在识别结束时给出相应的信息; 要与其他设备通信,它应该有几个标准的I / O端口。因此,语音压缩/解压缩,识别和I / O功能应该包含在芯片中。此外,最好根据SOC理念设计芯片,即在集成数字和模拟单元的单芯片中实现整个系统的功能。然后芯片仅需要电源,麦克风和扬声器就可以进行操作,这种系统体积小,成本低,可靠性高。

本文描述的语音识别系统是一个单片机,包含提示、回放、根据人说的话进行的短语训练和识别的语音功能。该芯片集成了一个8位微控制器(MCU)内核,片上RAM。片上ROM,ADC / DAC,带通滤波器,PWM,I / O端口和其他外围电路。MCU内核作为芯片的CPU,实现数字信号处理任务和系统控制。它是与行业标准8051微控制器兼容的目标代码。选择8051核心而不是DSP核心,是一把双刃剑。主要的好处是,这种8051内核的语音识别SOC成本至少比DSP内核低十倍。因此,它是低价消费产品的首选。但8051的数字信号处理能力是如此有限,以至于实现高性能的语音识别,也是一个挑战,即使是小词汇,孤立的单词的识别。不仅需要简化语音识别算法以适应8051的源限制,而且还需要一些有效的方法来克服应用系统的信道失真和低信噪比条件,这可能会导致性能的下降。应用系统经常遇到这些情况,以下段落描述了这些考虑因素。

本文的其余部分安排如下。在第2节中。我们描述了语音识别SOC的独特结构架构。在第3节中,描述了芯片的算法细节。测试板上的评估结果在第4节中给出。在上一节中,我们总结了语音识别SOC的性能和应用领域。

2、硬件架构

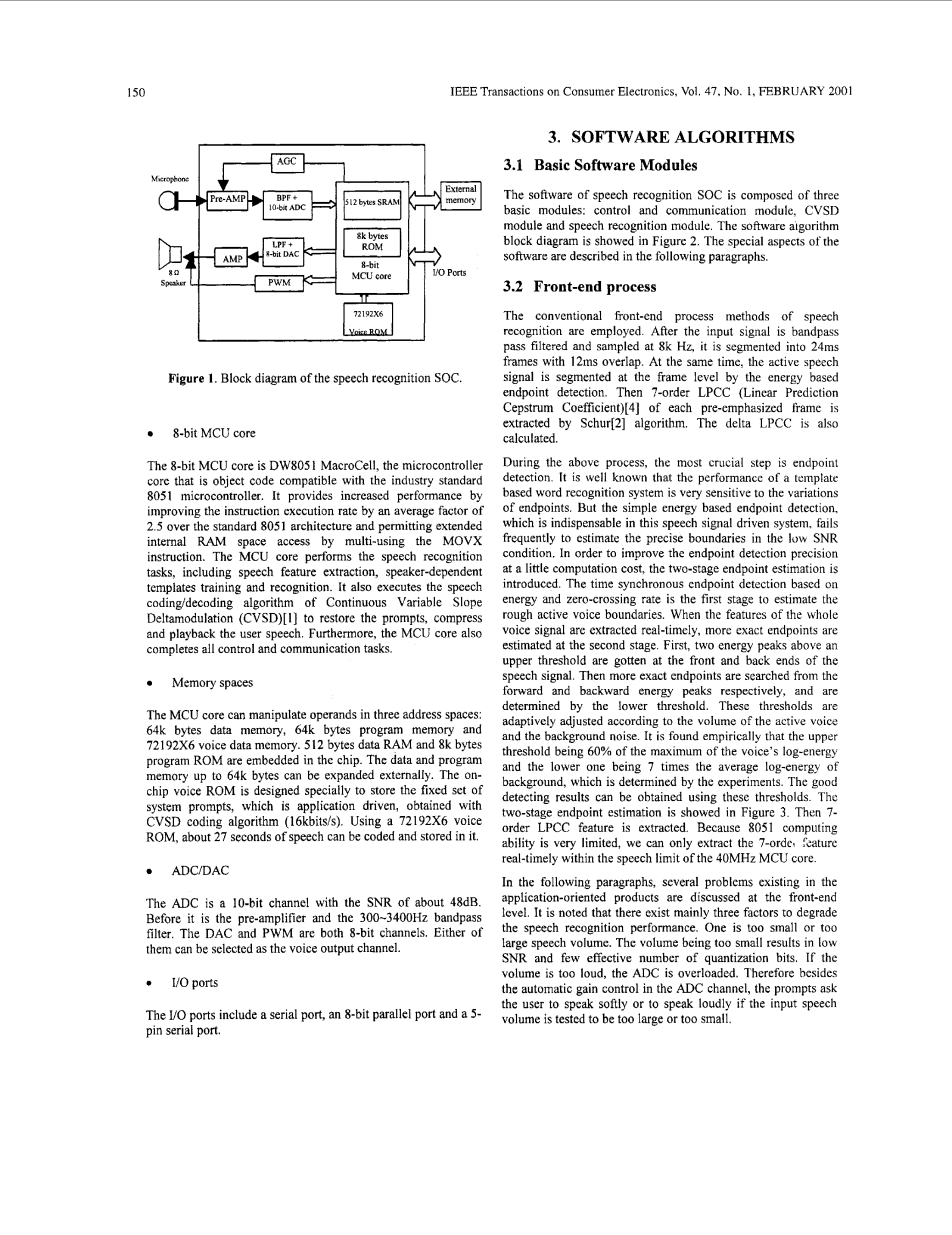

语音识别系统SOC具有独特的结构架构,由8位MCU内核,512字节片上RAM,8k字节片上ROM,72192x6位语音ROM,10位ADC / DAC,PWM(脉冲宽调制),以及通用I / O端口和其他外围电路组成。框图如图1所示。每个块的细节描述如下。

图1 语音识别SOC的框图

2.1 8位MCU内核

8位MCU内核是DW8051 MacroCell,它是与业界标准8051微控制器目标代码兼容的微控制器内核。与标准8051架构相比,它通过将指令执行速率提高了2.5倍,并通过多次使用MOVX指令允许扩展内部RAM空间访问,从而提高了性能。MCU内核执行语音识别任务,包括语音特征提取,扬声器相关模板训练和识别。它还执行连续可变斜率增量调制(CVSD)[1]的语音编码/解码算法,以恢复提示,压缩和回放用户语音。此外,MCU内核还完成所有控制和通信任务。

2.2 记忆空间

MCU内核可以对三个地址空间中的操作数进行操作:64k字节数据存储器,64k字节程序存储器和72192X6语音数据存储器。512字节数据RAM和8k字节程序ROM嵌入芯片中。可以在外部扩展高达64k字节的数据和程序存储器。片上语音ROM专门用于存储固定的系统提示语句,这是一种应用驱动、采用CVSD编码算法(16kbits / s)获得的。使用72192X6语音ROM,可以编码并存储大约27秒的语音。

2.3 ADC / DAC

ADC是一个10位通道,SNR约为48dB,它的前身是前置放大器和300~3400Hz带通滤波器。DAC和PWM均为8位通道。可以选择它们中的任何一个作为语音输出通道。

2.4 I / O端口

I / O端口包括一个串行端口,一个8位并行端口和一个5针串行端口。

3、软件算法

3.1 基本软件模块

语音识别软件SOC由三个基本模块组成:控制和通信模块,CVSD模块和语音识别模块。软件算法框图如图2所示。以下段落描述了该软件的特殊方面。

图2 语音识别SOC的算法框图

3.2 前端流程

采用传统的语音识别前端处理方法。在输入信号经过带通滤波并以8k Hz采样后,将其分段为24ms帧,重叠为12ms。同时,通过基于能量的端点检测在帧级对有效语音信号进行分段。然后通过Schur [2]算法提取每个预加重帧的7阶LPCC(线性预测倒谱系数)[4],并计算delta LPCC。

在上述过程中,最关键的一步是终点检测。众所周知,基于模板的单词识别系统的性能对端点的变化非常敏感。但是在低SNR条件下,这种基于能量的语音信号驱动系统中的简单终点检测经常无法估计出精确的边界。为了以较小的计算成本提高端点检测精度,我们引入了两阶段端点估计。基于能量和过零率的时间同步端点检测是估计粗略活动语音边界的第一阶段。当实时提取整个语音信号的特征时,在第二阶段就能估计更精确的端点。第一,在语音信号的前端和后端获得高于上阈值的两个能量峰值。然后分别从前向和后向能量峰值搜索更精确的端点,并由下限阈值确定。根据活动语音的音量和背景噪声自适应地调整这些阈值。根据经验发现,上限阈值是语音对数能量最大值的60%,而下限阈值是背景平均对数能量的7倍,这是由实验确定的。使用这些阈值可以获得良好的检测结果。两阶段终点估计显示在图3,然后提取7阶LPCC特征。由于8051的计算能力非常有限,我们只能在40MHz MCU内核的语音限制内实时提取7阶功能。

图3 两阶段端点检测

MAX:语音的最大对数能量。

Th2:第2阶段的上限,Th2=最大*比率。

THL:第二阶段的下限。

两阶段端点检测MAX:语音的对数能量的最大值。

Th2:阶段2中的上阈值,Th2 = MAX *比率。

Th1:阶段2中的下阈值。

在以下段落中,在前端级别讨论了面向应用程序的产品中存在的几个问题。注意,主要存在三个降低语音识别性能的因素。一个是太小或太大的语音量。音量太小会导致SNR变低并且降低有效的量化比特数。如果音量太大,则ADC过载。因此,如果测试的输入语音音量太大或太小,除了ADC通道中的自动增益控制之外,则需要提示用户轻声说话或大声说话。第二个因素是用户的嘴和麦克风驻极体之间的不同距离和方向。不同的说话距离首先影响语音的音量大小,同时头部位置的差异也会造成影响。因此,考虑到其确认的有效性和8位MCU核心的可接受的计算复杂度,我们使用CMS(倒谱均值减法)[3]方法。三个扬声器的语音在芯片组仿真板上进行实时测试,除了一个扬声器保持相额同的识别率,另外两个分别降低了29%和55%的错误率。第三个因素是不同的背景噪音,尤其是其他人说话的声音。我们通过芯片组仿真板的ADC通道在由数十人和计算机激活的办公室中记录输入短语。记录语音的SNR在-2dB~33dB范围内,78%短语在10dB以下。在这种情况下,平均识别率达到90%的水平。在安静的办公室录制时,平均信噪比高达20dB以上,95%短语高于10dB,平均识别率高达96%。因此,在该语音识别系统中应该使用一些降低噪声的语音识别方法来扩展其可用条件。但目前,但目前,语音增强对于一个8位单片机核心来说,技术是如此复杂,以至于系统只能测试输入短语的信噪比,并拒绝低的那一个,然后给出相应的提示。

3.3 段平均模板训练和识别

传统的动态规划(DP)方法,例如DTW(Dynamic Time Warping)算法[2]已经成功地用于单词识别系统,并且完成了高识别率(超过99%)。但是在语音识别SOC的MCU核心中实现DTW算法存在两个障碍。一个是过多的模板存储空间。100帧的DTW模板,每帧7阶LPCC,需要1.4k字节的存储空间。这需要太多的外部数据存储空间。另一个是模板匹配过程,它不可能实时地在MCU核心中执行。因此,不像DTW那样直接从每个语音帧生成模板,使用模板的片段均值方法。基本思想是根据倒谱的方差对语音进行分段,并对每个段的特征向量求平均值。然后连接片段均值特征向量形成参考模板。采用这种方法,模板和模板匹配空间的存储空间量都大大减少。平均段长度是8帧语音信号。因此,大约10个段被分为语音,持续时间为1秒。然后,只需要280个字节来存储模板的7阶LPCC及其动态变化。存储空间仅为之前所需的存储空间的四分之一。

众所周知,仅从一个令牌生成的模板不够健壮。此外,在该识别系统中易于出现端点估计误差和分段缺省。所以[4]中提到的顺序训练方法用来。段顺序模板在顺序培训中更新。为了获得第二一致令牌,要求用户第二次说出训练短语。然后,通过DP过程比较第一参考模板和第二令牌,并将得到的失真分数与阈值进行比较,以确定第二令牌是否与参考模板一致。如果得分小于阈值,则接受第二令牌以根据DP过程获得的状态分段来计算第二段平均模板。然后将最终模板计算为两个临时参考模板的平均值,并播放成功训练的提示。训练成功。如果失真分数大于阈值,则播放训练失败提示,并可在其他时间对短语进行训练。

通过顺序训练方法,由段平均模板引起的性能下降得到了相当大的补偿。使用不同模板的三种不同识别系统(即DTW模板,分段平均模板和顺序训练的分段平均模板)的性能在语音数据库上与三个扬声器的8个移动电话语音命令进行比较。使用的语音数据通过芯片组仿真板的输入实际通道记录,但所有计算都在PC平台上完成。结果如表1所示。

表1三种模板的识别率比较

扬声器3的发音变化远远超过其他两个,因此即使是DTW模板也不能很好地工作。但顺序训练相对提高了模板的鲁棒性,结果令人满意。

我们遵循两个步骤。首先,通过DP过程计算输入短语和模板的失真分数。其次,选择具有最小测量距离的类作为识别结果。使用具有路径约束的维特比搜索算法,其被认为对于段平均模板匹配是优选的。为了消除维特比搜索过程中的冗余计算,仅在约束区域中计算局部得分,如图4所示。

图4 路径约束维特比算法的计算区域

两个参数,即上部宽松宽度和路径约束宽度,控制搜索区域的范围。首先,计算中心匹配路径的局部失真分数,该分数在当前测试帧的情况下,如果分数小于当前模板帧计算的分数,则立即转换到下一个模板帧。如果当前测试帧与当前模板帧的失真分数较小,则最佳路径仍占用当前模板帧。上部松散宽度确定中心路径上方的搜索区域,并且路径约束宽度确定整个区域。

很明显,如果规定的宽度较大,则全局最优路径更可能包含在约束区域中,但搜索过程花费更多时间。上部宽松宽度的影响小于路径约束宽度。当下部空间不受约束且上部宽松宽度等于2时,与正确单词的强制对齐的分割相比,没有分割差异。当上松宽度等于1时,与全空间维特比搜索的分割相比,具有不同分割的3.7%正确令牌。在各种路径约束宽度下具有错误分段的令牌百分比和得到的平均相对失真分数误差在图5中示出。实际宽度应该是小值和大值之间的权衡。如果使

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[20483],资料为PDF文档或Word文档,PDF文档可免费转换为Word