基于PROTEUS的ARM虚拟实验平台的设计外文翻译资料

2022-09-06 11:37:41

英语原文共 40 页,剩余内容已隐藏,支付完成后下载完整资料

LPC2114/2124使用指南

- 概述

LPC2114/2124是基于一个支持实时仿真和跟踪的16/32位ARM7TDMI-STM CPU的微控制器,并带有128/256 k字节(kB)嵌入的高速Flash存储器。128位宽度的存储器接口和独特的加速结构使32位代码能够在最大时钟速率下运行。对代码规模有严格控制的应用可使用16位Thumb模式将代码规模降低超过30%,而性能的损失却很小。

由于LPC2114/2124较小的64和144脚封装、低功耗、多个32位定时器、4路10位ADC、多PWM通道以及多达9个外部中断引脚的46个GPIO线路,这些微控制器特别适用于工业控制、医疗系统、访问控制和POS机。由于内置了宽范围的穿行通信接口,它们也非常适合于通信网关、协议转换器、嵌入式软modern以及其它各种类型的应用。

注意事项:贯穿整个数据表,术语LPC2114/2124将应用于设备中可带有/00或/01的尾标。在有必要的情况下,/00或/01尾标将被用来区分其他的设备。

- 特性

2.1 LPC2114/2124/01的主要特性

- 快速GPIO端口能使端口引脚比原始装置快3.5倍。不管它的功能,GPIO同样允许一个端口引脚在任何时候被读。

- ADC专用结果寄存器向上减少了中断。当被用于数字I/O功能时,ADC垫的最大承受电压是5V。

- UART0/1包括分数阶传输速率发生器,自动变频能力和在硬件上全面实行的握手流量控制。

- 缓冲SSP串行控制器支持SPI,4线SSI和微格式。

- SPI可编程的数据长度和控制模式增加。

- 多样的CRPC代码读保护使不同安全水平被实行。这个特性在LPC2114/2124/00装置中也可获得。

- 一般目的定时器可用于外部计数器。

2.2 所有装置的主要特征

- 16/32位64/144脚ARM7TDMI-S微控制器。

- 16K字节静态RAM。

- 128/256K字节片内Flash程序存储器。128位宽度接口/加速器实现高达60MHz的操作频率。

片内Boot装载程序实现在系统编程(ISP)和在应用中编程(IAP)。Flash编程时间:1ms可编程512字节,扇区擦除或整片擦除只需400ms。

- EmbeddedICE-RT接口使能断点和观察点。当前台任务使用片内RealMonitor软件调试时,中断服务程序可继续执行。

- 嵌入式跟踪宏单元(ETM)支持对执行代码进行无干扰的高速实时跟踪。

- 4路10位A/D转换器,转换时间低至2.44us。

- 2个32位定时器(带4路捕获和4路比较通道)、PWM单元(6路输出)、实时时钟和看门狗。

- 多个串行接口,包括2个16C550工业标准UART、高速I2C接口(400 kbit/s)和2个SPI接口。

- 在设置时间100ms内通过片内PLL可实现最大为60MHz的 CPU操作频率。

- 向量中断控制器。可配置优先级和向量地址。

- 多达46个通用I/O口(可承受5V电压),9个独立外部中断引脚。

- 片内晶振频率范围:1~30 MHz。

- 2个低功耗模式:空闲和掉电。

- 通过外部中断将处理器从掉电模式中唤醒。

- 可通过个别使能/禁止外部功能来优化功耗。

- 双电源:

-CPU操作电压范围:1.65~1.95 V(1.8 V /- 8.3%)

-I/O操作电压范围:3.0~3.6 V(3.3 V /- 10%) 在承受电压5V的I/O垫上。16/32位ARM7TDMI-S处理器 。

3器件信息

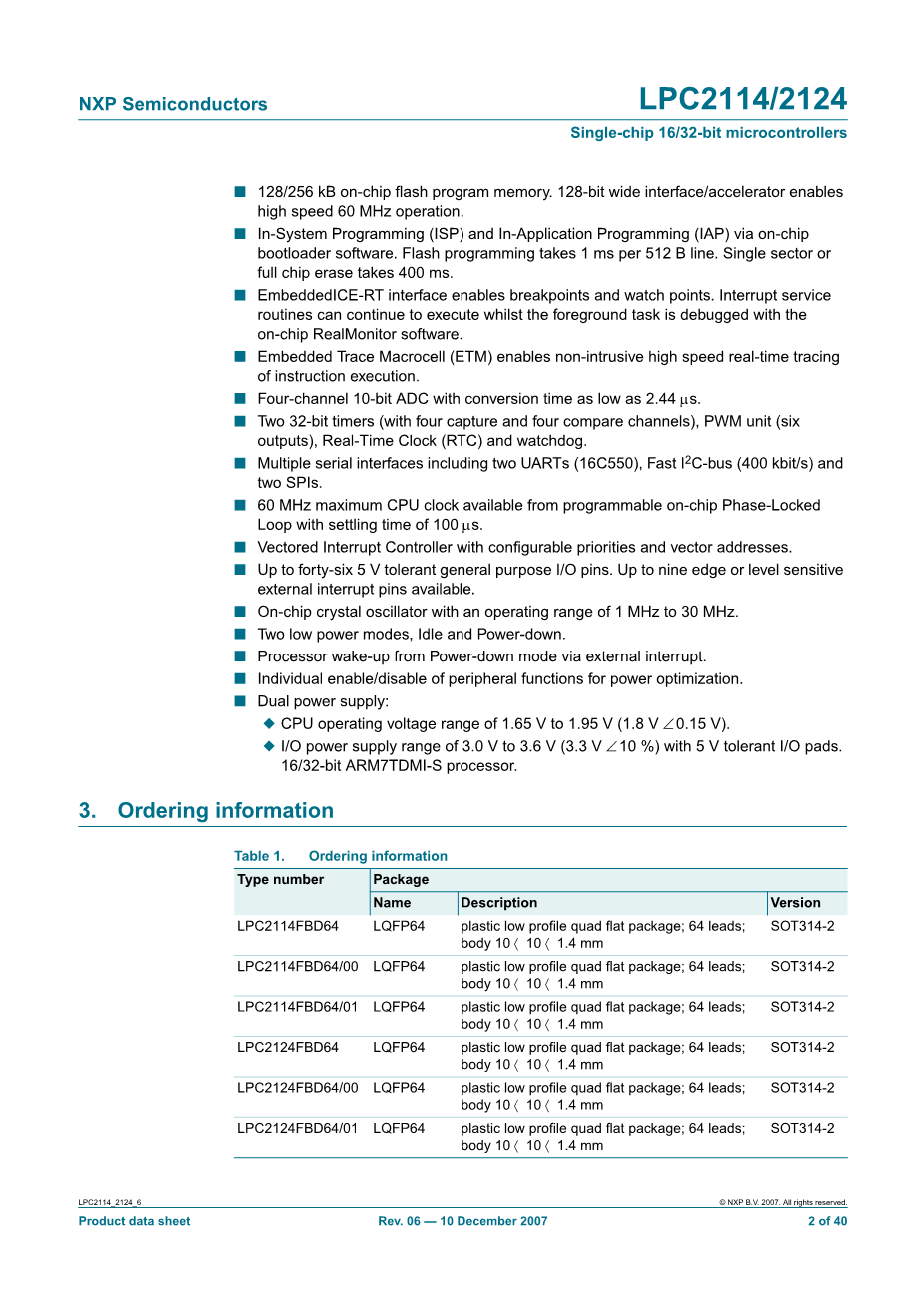

Table 1. Ordering information

|

Type number |

Package |

||

|

Name |

Description |

Version |

|

|

LPC2114FBD64 |

LQFP64 |

plastic low profile quad flat package; 64 leads; body 10 ′ 10 ′ 1.4 mm |

SOT314-2 |

|

LPC2114FBD64/00 |

LQFP64 |

plastic low profile quad flat package; 64 leads; body 10 ′ 10 ′ 1.4 mm |

SOT314-2 |

|

LPC2114FBD64/01 |

LQFP64 |

plastic low profile quad flat package; 64 leads; body 10 ′ 10 ′ 1.4 mm |

SOT314-2 |

|

LPC2124FBD64 |

LQFP64 |

plastic low profile quad flat package; 64 leads; body 10 ′ 10 ′ 1.4 mm |

SOT314-2 |

|

LPC2124FBD64/00 |

LQFP64 |

plastic low profile quad flat package; 64 leads; body 10 ′ 10 ′ 1.4 mm |

SOT314-2 |

|

LPC2124FBD64/01 |

LQFP64 |

plastic low profile quad flat package; 64 leads; body 10 ′ 10 ′ 1.4 mm |

SOT314-2 |

3.1器件选项

Table 2. Ordering options

|

Type number |

Flash memory |

RAM |

Fast GPIO/SSP/ Enhanced UART, ADC, Timer |

Temperature range |

|

LPC2114FBD64 |

128 kB |

16 kB |

no |

-40 °C to 85 °C |

|

LPC2114FBD64/00 |

128 kB |

16 kB |

no |

-40 °C to 85 °C |

|

LPC2114FBD64/01 |

128 kB |

16 kB |

yes |

-40 °C to 85 °C |

|

LPC2124FBD64 |

256 kB |

16 kB |

no |

-40 °C to 85 °C |

|

LPC2124FBD64/00 |

256 kB |

16 kB |

no |

-40 °C to 85 °C |

|

LPC2124FBD64/01 |

256 kB |

16 kB |

yes |

-40 °C to 85 °C |

6功能描述

LPC2114/2124系统的细节以及次要的功能在以下部分被描述。

6.1 结构概述

ARM7TDMI-S是通用的32位微处理器,它具有高性能和低功耗的特性。ARM结构是基于精简指令集计算机(RISC)原理而设计的。指令集和相关的译码机制比复杂指令集计算机要简单得多。这样使用一个小的、廉价的处理器核就可实现很高的指令吞吐量和实时的中断响应。

由于使用了流水线技术,处理和存储系统的所有部分都可连续工作。通常在执行一条指令的同时对下一条指令进行译码,并将第三条指令从存储器中取出。

ARM7TDMI-S处理器使用了一个被称为THUMB的独特结构化策略,它非常适用于那些对存储器有限制或者需要较高代码密度的大批量产品的应用。

在THUMB后面一个关键的概念是“超精简指令集”。基本上,ARM7TDMI-S处理器具有两个指令集:

- 标准32位ARM指令集

- 16位THUMB指令集

THUMB指令集的16位指令长度使其可以达到标准ARM代码两倍的密度,却仍然保持ARM的大多数性能上的优势,这些优势是使用16位寄存器的16位处理器所不具备的。因为THUMB代码和ARM代码一样,在相同的32位寄存器上进行操作。

THUMB代码仅为ARM代码规模的65%,但其性能却相当于连接到16位存储器系统的相同ARM处理器性能的160%。

6.2片内FLASH程序存储器

LPC2114/2124分别集成了一个128K和256K的FLASH存储器系统。该存储器可用作代码和数据的存储。对FLASH存储器的编程可通过几种方法来实现。它可以在系统中通过串行接口被编程。使用在应用编程的应用程序也可以在应用程序运行时对FLAH进行擦除和/或编程,这样就为数据存储和现场固件的升级都带来了极大的灵活性。当引导装载程序被使用,120KB和248KB的FLASH存储器可被用户代码获得。

LPC2114/2124FLASH存储器提供一个最小10万次的擦除/编程循环和20年的数据保留。

片内引导装载程序(自1.60版以来)为LPC2114/2124提供代码读访问保护(CRP)。当CRP 被激活,JTAG调试端口和片内RAM或FLASH存储器的ISP指令失去功能。

然而,ISP FLASH擦除指令在任何时候能被执行(不论CRP是开还是关)。整个片内用户FLASH的消除能实现CRP的消除。当CRP被关闭,通过JTAG或ISP访问芯片的所有方法将被修复。

6.3片内静态RAM

片内静态RAM可用作代码和数据的存储。SRAM支持8位、16位和32位访问。LPC2114/2124提供16KB的静态RAM。

6.4存储映像

LPC2114/2124存储映像包括几个确切的区域,表格3有所显示。

另外,CPU中断向量可能重新被绘制使得他们存在于FLASH存储器(系统默认值)或片内静态RAM中。6.17节“系统控制”部分有描述。

6.5中断控制器

向量中断控制器(VIC)接受所有中断请求输入并将它们分为FIQ、向量IRQ和非向量IRQ像可编程设置定义的那样。可编程分配机制意味着不同外设的中断优先级可以动态分配并调整。

快速中断请求(FIQ)要求具有最高优先级。如果分配给FIQ的请求多于1个,VIC将中断请求“相或”后向ARM处理器产生FIQ信号。当只有一个中断被分配为FIQ时可实现最短的FIQ等待时间,因为FIQ服务程序只要简单地启动器件的处理就可以了。但如果分配给FIQ级的中断多于1个,FIQ服务程序从VIC中读出一个字来识别产生中断请求的FIQ中断源是哪一个。

向量IRQ具有中等优先级。该级别可分配16个中断请求。任意一个中断请求都可分配到16个向量IRQ slot中的任意一个,其中slot0具有最高优先级,而slot15则为最低优先级。

非向量IRQ的优先级最低。

VIC将所有向量和非向量IRQ“相或”向ARM处理器产生IRQ信号。IRQ服务程序可通过读取VIC的一个寄存器立即启动并

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[146896],资料为PDF文档或Word文档,PDF文档可免费转换为Word