基于FPGA的振动数据采集系统的设计毕业论文

2020-03-20 23:51:40

摘 要

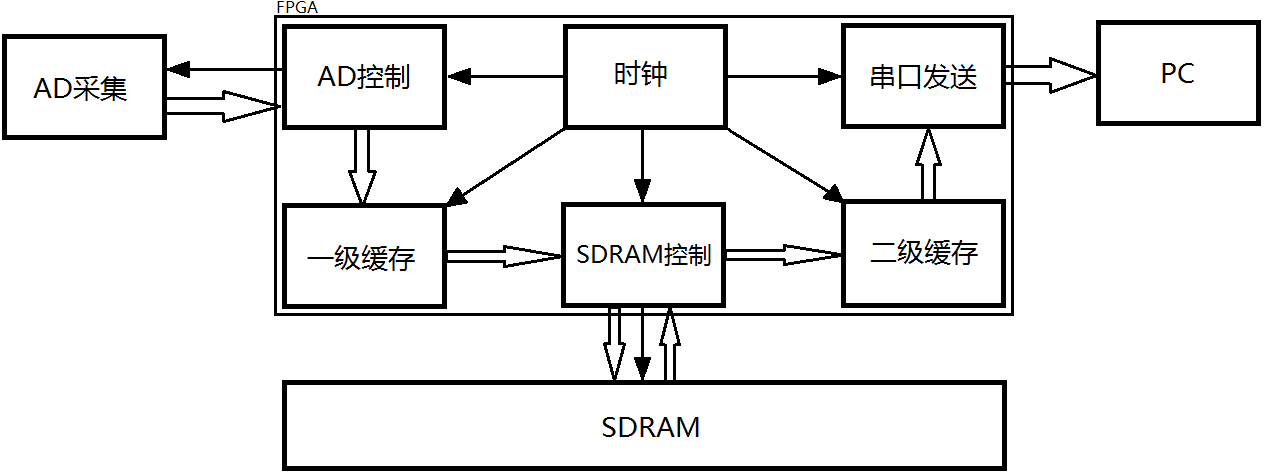

中国制造2025提出了智能制造的要求。用智能制造提高生产力,数据采集作为整个自动化流程的最前端,是不可缺少的重要环节。论文主要针对生产现场的振动信号,研究了如何在FPGA的控制下采集、存储、发送所接收到的模数转换数据,主要性能指标在于高速、大容量。设计主要内容为使用Quartus II软件编写系统verilog 程序;在Qsys设计器中配置一个Nios II软核系统,将数据以串行方式转发到PC机。关键技术在于数据存储与发送的时序配合,采用状态机圆满完成这一控制任务。此外,由于Qsys设计器提供了RS232发送组件,串口发送模块的设计不再是难点。在Modelsim软件中观察系统总体仿真波形与调试输出,观察到系统成功完成了数据采集与发送任务。工作的特色在于使用FPGA片内的CPU软核Nios II,相比于外设微控制器,前者完全具备性能与成本上的优势。研究结果表明,相比于传统微控制器,使用FPGA进行高速数据采集,不但具备可行性,还具有很大的优越性。这为拓展研究更多功能,更高性能的新一代振动数据采集系统打下了坚实基础。

关键词:FPGA;Nios II;verilog;RS232

Abstract

Made in China 2025 put forward the requirements of smart manufacturing. With smart manufacturing to increase productivity, data collection is the most important part of the entire automation process. The paper mainly focuses on the vibration signals of the production site, and studies how to acquire, store, and send the received analog-to-digital conversion data under the control of the FPGA. The main performance indicators are high speed and large capacity. The main content of the design is to use the Quartus II software to write the system verilog program; configure a Nios II soft-core system in the Qsys designer to forward the data serially to the PC. The key technology lies in the timing of data storage and transmission, and the state machine successfully completes this control task. Since the Qsys designer provides RS232 sending components, serial port sending is no longer difficult. Observe the overall system simulation waveform and debug output in Modelsim software and observe that the system has completed the data collection and transmission tasks. The job feature is the use of an on-chip CPU soft-core Nios II, which offers full performance and cost advantages over peripheral microcontrollers. The research results show that using FPGA for high-speed data acquisition is not only feasible but also has great advantages over traditional microcontrollers. This lays a solid foundation for further research into more functions and a new generation of higher performance vibration data acquisition systems.

Key Words:FPGA;Nios II;verilog;RS232

目录

1. 绪论 1

1.1 课题背景与意义 1

1.2 国内外的研究现状 2

1.3 论文内容安排 4

2. 设计方案 5

2.1 设计方案选择 5

2.2 系统硬件方案 5

2.3 总体设计方案 6

3. 系统硬件设计 7

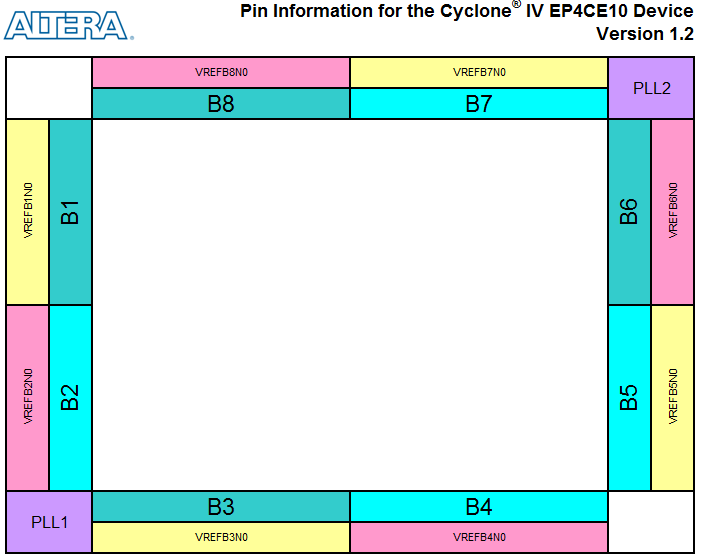

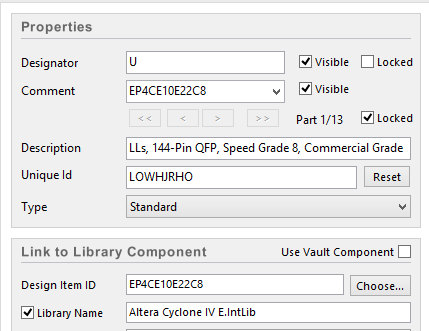

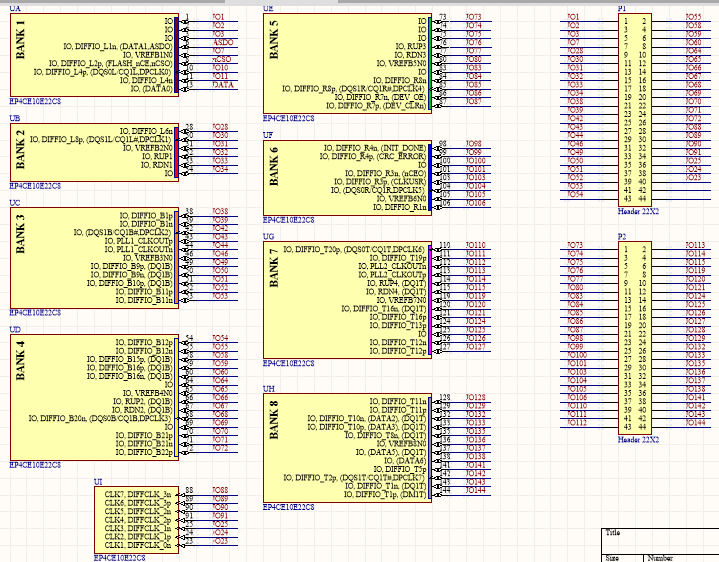

3.1 FPGA电路 7

3.1.1 FPGA芯片介绍 7

3.1.2 FPGA用户IO接口电路 8

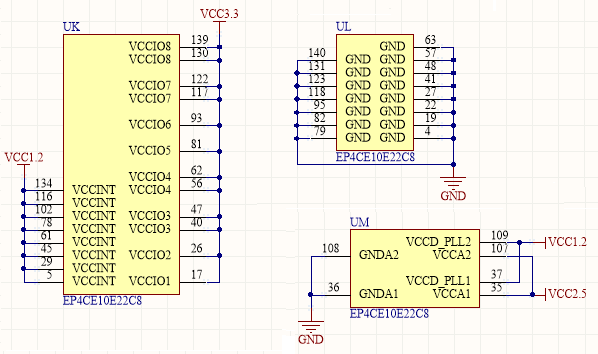

3.1.3 FPGA电源电路 8

3.1.4 FPGA晶振电路 9

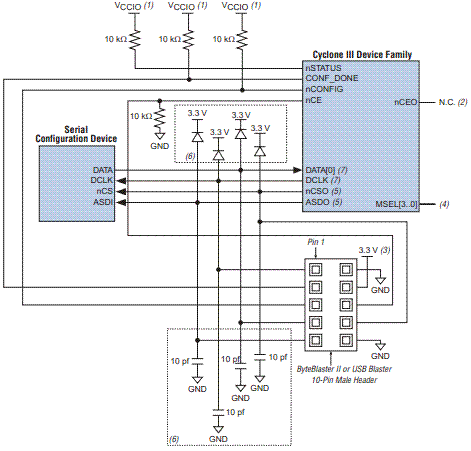

3.1.5 FPGA下载配置电路 9

3.2 传感器与调理电路 11

3.2.1 振动测量工艺 11

3.2.2 仪用放大器电路 12

3.3 AD9288电路 13

3.3.1 AD9288介绍 13

3.3.2 AD9288电路 15

3.4 SDRAM存储电路 16

3.4.1 SDRAM介绍 16

3.4.2 SDRAM存储电路 17

3.5 TRS3232电路 18

3.6 电源及滤波电路 19

4. 系统软件设计 20

4.1 时钟模块 20

4.1.1 PLL介绍 20

4.1.2 程序与仿真 21

4.2 AD驱动模块 22

4.3 数据存储缓存模块 23

4.3.1 FIFO介绍 23

4.3.2 有限状态机介绍 23

4.3.3 程序与仿真 24

4.4 SDRAM驱动模块 25

4.4.1 SDRAM时序介绍 25

4.4.2 程序仿真 26

4.5 数据发送缓存模块 28

4.6 RS232发送模块 29

4.6.1 Nios II软核系统搭建 29

4.6.2 程序仿真 30

4.7 系统总体调试 31

5. 总结与展望 33

参考文献 34

附录A 系统电路图 35

附A1 FPGA 主电路图 35

附A2 FPGA 配置电路图 36

附A3 AD9288电路图 37

附A4 其他电路图 37

附录B FPGA程序 38

附B1 时钟模块 38

附B2 AD9288驱动程序 39

附B3 数据存储缓存程序 40

附B4 SDRAM驱动程序 43

附B5 数据发送缓存程序 47

附B6 串口发送程序 50

附B7 系统顶层程序 59

附B8 系统测试程序 61

致谢 64

- 绪论

- 课题背景与意义

作为自然界普遍存在的一种自然现象,振动与人们的生活息息相关。且不论声音由振动产生,为人类生产各类物资的动力设备也离不开振动这项重要参数。如流水线上车床的运转,各式交通工具的运行,雷达声纳等高精尖设备的检测。在上述项目为典型的工程技术应用中,无论是利用振动还是防止振动都需要对振动做一定的采集与检测。

只有采集到有效的数据信息,工程人员才能做出合理的分析与判断。因此,振动数据采集系统要对应用场合有强大的适用性。为了满足课题所提出的高速、大容量的采集目标,便需要设计合理的软硬件系统。

作为衡量数据采集系统采集能力的重要指标,采样精度受限于系统中采用的AD/DA转换器件。更快的采样频率,更高的的转换精度与分辨率,都是高速系统所需要的。目前以MCU、DSP、FPGA等芯片为主控制器的数据采集系统各有应用,在它们的控制下模数/数模转换等器件才能协同工作。MCU,即单片(微型计算)机,或称微控制器。它是中央处理器CPU、IO接口、存储器、定时/计数器、中断系统等电路单元受惠于超大规模集成电路技术的成果。具有体积小,功耗低,结构简单,嵌入开发容易,功能发展迅速,控制能力强等特点。DSP,即数字信号处理,它非常擅长数字信号在高速下的运算与处理,如数字滤波,频谱分析等。它具有实现高速运算所需的硬件架构与指令集,对复杂算法与大流量数据的处理能力极强。FPGA,即现场可编程门阵列,它是一种半定制电路,在解决了定制电路不满足特定功能需求的同时,又解决了原有可编程器件硬件资源有限的缺点。它具有IO接口丰富、逻辑连接灵活、硬件并行计算等特点。经过简单的编译、综合、适配、下载,就可以烧录到FPGA芯片上进行测试。

MCU与DSP的工作方式属于顺序执行,自身具有指令集的架构使其实时响应控制与复杂运算能力强,存在指令周期却使其高频时序控制力较弱;FPGA与之相反,无指令集的架构也无指令周期的制约,时序控制能力强。与传统CPU相比,FPGA不再是顺序执行,而是真正的并行执行,在硬件并行的优势下,FPGA具有更高的执行速度和工作效率,每个时钟周期能完成更多的处理任务。一般来说,CPU可以实现的功能,FPGA也可以以硬件设计的方法来完成。但是,太过复杂的算法用硬件设计来实现比较困难,资源消耗也大。对此问题FPGA提供了内部CPU软核Nios II,使FPGA设计者不需要再增加外部CPU,兼顾了系统的工作性能与投入成本。在工程设计中系统的需求随时可能发生变动,改变设计时,FPGA属于可编程器件而非定制电路,降低了系统变更时产生的硬件成本,在开发与维护方面更加灵活。总之,从性能与成本方面综合考虑,FPGA更适合应用于高速采集,本文将对此做研究与设计。

- 国内外的研究现状

数据采集是指从传感器或者其他待测模拟与数字单元,采集电量或非电量信号送到上位机进行分析与处理。中国制造2025提出了智能制造的要求,用智能制造提高生产力,数据采集作为整个自动化流程的最前端,是不可缺少的重要环节。

国外振动数据采集器起步早,发展快,从近来国外公司发布的产品来看,振动数据采集器主要朝体积优化、功能多样、易于操作等方面发展。国外FLUKE公司推出的262XA系列数据采集器,有21路模拟输入通道,8路数字输入/输出,另外4路用于报警输出;使用PCMCIA卡作为存储,存储容量可选;可同时使用交直流电源,断电时自动切换至直流;RS232接口与PC通信,记录的数据格式与Lotus,Excel相兼容;开发商还提供系统软件供用户在远程PC控制采集系统或直接在仪器屏幕上展示数据趋势曲线。惠普公司生产的HP34970A型数据采集器,可配置成20-120个通道,拥有6位半分辨率,0.004%的基本直流精度,250通道/秒的扫描速率,5万个读数存储,断电时数据可保持,标准HP-IB与RS232接口。Solartron公司的IMP系列分散式数据采集器具备优良的抗噪和共模隔离能力,内置24位高精度AD测量,在功耗低、体积小、环境要求低等方面十分优秀。

国内方面,由于技术水平,特别是线路工艺,成品芯片等方面的不足,整体水平一度落后于人。以国内北京万博振通公司研发的BVM-100系列振动数据采集器为例,它拥有液晶显示屏,全中文显示界面,双通道同步采集,USB标准串口通信接口;可存储/回放1024点,200组双通道数据;16位AD采样,动态范围达到144dB。采样频率每通道最高1MHz(双通道同步),自动量程选择,体积小(190*150*64mm),重量轻(1500g)。它虽然在工程应用方面达到了较高水平,但是仍然存在容量较小,现场处理能力弱,设备软件的功能水平低等问题有待解决。北京法易德测控推出的STD510型振动数据采集器,具有24位AD采样精度,使用DSP处理器;振动测量范围为0.5~100mm/s,分析频率范围为5~5000hz;内置8M存储,可存储3000组数据;USB接口与PC机通讯;此外还具备屏幕波形显示、10小时电池待机、防水防尘防磁等能力。

经过对比国内外已投入商用的振动数据采集器,可发现它们并没有配备到传感器这一级器件,需要用户另行采购配置。振动传感器,又称换能器,拾振器,本质上是一种机电转换装置。振动传感器并不直接进行机电转换,而是先接收外部振动,将之转换为一定标准的机械量后,再进行机电变换得到输出量。随着新技术的发展与新材料的应用,振动传感器的结构与原理也在不断更新。

振动传感器的机械接收变换方式从相对式到惯性式,扩展了振动传感器的应用范围。前者传感器与被测物分别处于两个参考系/固定点上,所测量的是被测物相对于传感器的相对运动。在一些特殊的测量场合,如行驶的机车整体的振动,飞行器外壳的振动等,无法找到相对于被测物的固定的参考点,这时必须使用后者进行测量。在惯性式机械测振中,传感器固定在被测物上,所测量的是惯性质量块与被测物之间的相对运动。

在机电转换方式上,国外振动传感器以压电式居多。它利用压电材料的压电效应(某些电介质物体在某个方向受到压力或拉力作用时,表面会产生电荷)。由于压电效应产生的电荷量与加速度成正比,因此压电式传感器又称为加速度传感器,它的测量精度相对较高。国内的振动传感器种类繁多,以电涡流式、电感式、电容式等为众,但都属于磁电方式。由于产生的电荷量与速度成正比,因此此类传感器又称为速度传感器。其结构相对简单,成本低而测量精度较差。

国内外现有的振动数据采集器,在技术细节上可分为多种设计方案。

在数据存储方式上,各式振动数据采集器可分为三种。第一种即测即显,内置较大容量缓存以满足工程需求,通常为现场测试人员手持使用,如国内北京万博振通公司研发的BVM-200测振仪。第二种使用RAM存储器,可以采集到存储器容量的数据。目前发展到的DDR4 SDRAM频率可达4266Mhz、容量可达128GB、功耗也显著降低。为了节省数据传输的时间,第三种方式直接使用DMA(直接存储器访问)方式。顾名思义,在数据收发的不同时刻,DMA控制器与PC机分别拥有对存储空间的控制权,目标设备可以直接访问存储器而不需要CPU的干预,因而数据传输率极高。国外FLUKE公司的262XA系列即采用这一存储/传输方式。

在主控单元上,单片机、DSP、FPGA各有应用。单片机又译作微控制器,适合实时控制,擅长响应外部中断处理。其特长在于控制而非高速。尽管有专为高速而设计的STM、AVR、STC等系列单片机,但单片机内部的指令周期、指令集是其无法回避的存在,在复杂而高速的数据传输或通信领域,单片机显得力不从心。DSP即数字信号处理,与大多采用冯诺依曼结构的单片机不同,DSP采用程序与数据分离的哈佛结构,而且在一个指令周期内就能够完成一次加法与乘法。适合应用于低采样/输入速率下的密集算法或大数据流处理。当工作频率过高时,DSP首先会存在高频干扰,其次每个指令周期能完成的计算量会极大地降低。与属于CPU的MCU、DSP不同,FPGA为硬件并行结构,没有指令周期与指令集,片内大量硬件逻辑资源组成的查找表结构,使FPGA可以以并行处理的方式快速处理大量数据。典型的应用于,图像处理、高速数据处理等密集通信任务。在一些高速采集系统中,同时使用了FPGA与MCU。利用MCU实时控制与复杂算法能力强的特点,将之作为主控制器,负责控制FPGA工作以及远程通信任务。FPGA则专心用于处理高采样速率下产生的密集数据。这样的协同工作方式发挥了FPGA与MCU的特长,但在保证了高速系统工作性能的条件下,不可避免地带来了系统成本上的提高。针对这一需求,FPGA厂商推出了嵌在FPGA芯片内部的CPU软核,即Nios II处理器。这样FPGA就能以硬件逻辑资源和Nios II软核协同工作,不需要再外设MCU。由此可见,使用FPGA来设计高速采集系统具备极大的灵活性,在较低成本的前提下能得到高性能。

在数据传输方式上,典型的应用有RS232、USB、以太网、DMA方式等。RS232作为早期的一种串行通讯协议,应用较为广泛,但传输速率缓慢。在15米距离上,RS232传输速率会降至20Kb/s。但随着传输距离的缩减,这个速率会逐渐提升。USB由1.0版本发展到3.0版本,传输速率分别达到1.5Mb/s、480Mb/s、5Gb/s。USB需要编写通信协议与驱动程序,在工程应用中通常直接使用EZ-USB等集成USB模块。以太网能够使区域所有设备,在局域网内以10-1000Mb/s的速率传输数据,适合于规模工作,对于工程单点检测与采集来说成本较高。DMA方式如前所述,是一种方便的直接存储器访问技术,用户可以根据需求,自行更换不同容量的存储卡。

在微电子、通信等高新电子技术迅猛发展与实际工程需求的双重影响下,数据采集系统向着多功能、多用途、高性能、便携式、高环境适应性、易开发维护等方面发展。经过对比国内外市场推出的振动数据采集器的采集速率、存储深度、系统功能、价格等条件,可见作为技术上的后发者,国内振动数据采集系统的市场投入产品虽然和国外成熟产品相比还有一定差距,但研究出一套性价比高,功能强力,小巧易用的振动数据采集系统不失为市场竞争的有效手段,同时也为拓展研究更多功能,更高性能的新一代振动数据采集系统打下了坚实基础。

论文内容安排

第一章绪论,对课题的背景与意义做先一步研究,再探索国内外研究现状。

第二章设计方案,先介绍硬件结构、软件逻辑,再展示系统总体方案。

第三章系统的硬件设计。介绍FPGA芯片电路、振动信号传感器与调理电路、模数转换器电路、外部存储电路、RS232电平转换器电路以及电源和滤波等电路。

第四章系统的软件设计与仿真。按照FPGA控制下的数据流向,从时钟模块开始,对模数转换模块、一级(数据存储)缓存模块、SDRAM驱动模块、二级(数据发送)缓存模块、串口发送模块一一作说明与仿真。

第五章总结与展望。

第六章附件。包含硬件电路图、FPGA软件程序。

设计方案

设计方案选择

方案一:

采用Altium Designer完成系统软硬件设计。Altium Designer作为一款电子设计自动化(Electronic Design Automation)工具,完美融合了原理图设计、电子电路仿真、PCB绘制编辑、拓扑逻辑自动布线、信号完整性分析等功能。设计者只需要一个软件就能简洁高效地完成FPGA设计与电子线路设计。但是由于众识对其印象停留在EDA领域,对其FPGA设计能力鲜有关注,再加之厂商推出的FPGA软件与芯片契合度高。因此自学成本高,费而不惠。

方案二:

以上是毕业论文大纲或资料介绍,该课题完整毕业论文、开题报告、任务书、程序设计、图纸设计等资料请添加微信获取,微信号:bysjorg。

相关图片展示: